### **C-DAC Four Days Technology Workshop**

ON

Hybrid Computing – Coprocessors/Accelerators Power-Aware Computing – Performance of Application Kernels

hyPACK-2013

(Mode-4 : GPUs)

# **Classroom lecture :** An Overview of GPGPUs /GPU Computing

Venue : CMSD, UoHYD ; Date : October 15-18, 2013

### An Overview of GPGPUs /GPU Computing

#### Lecture Outline

Following topics will be discussed

- ✤ An Overview of GPUs Past Developments GPU Prog.

- An overview of CUDA enabled NVIDIA GPUs OpenACC CUDA 5.5 &

- An Overview of AMD GPUs Programming OpenCL

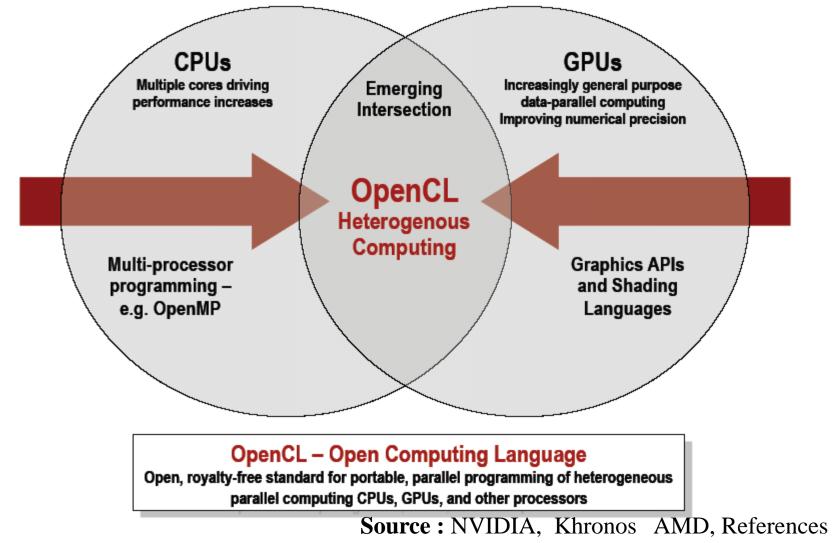

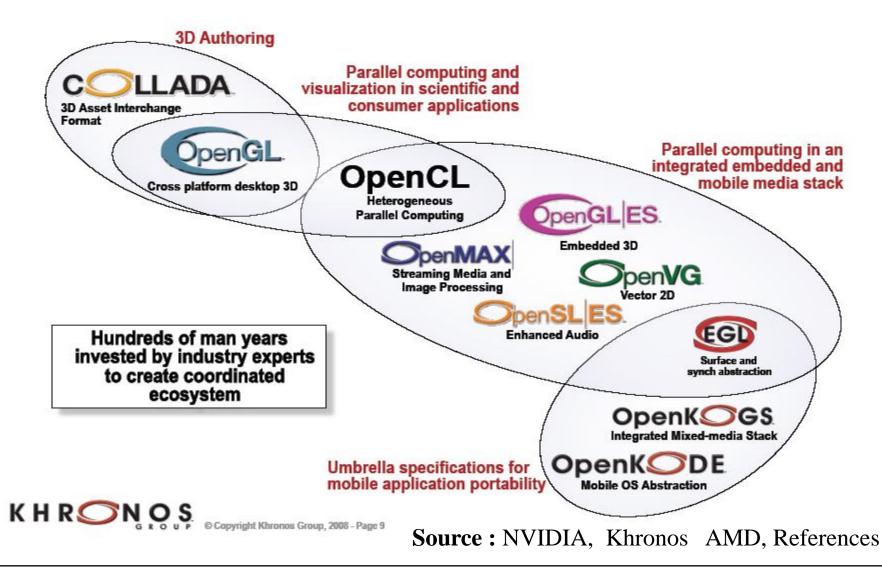

- ✤ An Overview of OpenCL Heterogeneous Prog.

**Source :** References given in the presentation

# Part-I (A)

# An Overview of GPUs / Past – GPU Programming on GPUs

Source & Acknowledgements : NVIDIA, AMD, References

C-DAC hyPACK-2013

## Overview

- What is GPU ? Graphics Pipeline

- GPU Architecture

- GPU Programming OpenGL, DirectX, NVIDIA (CUDA), AMD (Brook+)

- Rendering pipeline on current GPUs

- Low-level languages

- Vertex programming

- Fragment programming

- High-level shading languages

- GPU Architecture Graphics Programming

#### Source : References

- From Wikipedia : A specialized processor efficient at manipulating and displaying computer graphics

- ✤ 2D primitive support bit block transfers

- Some might have video support

- And of course 3D support (a topic at the heart of this presentation)

- GPUs are optimized for raster graphics

#### Source : References

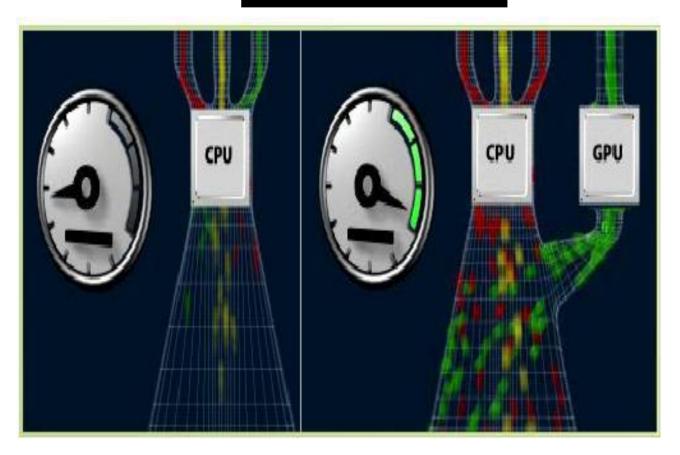

Without GPU

With GPU

**Source :** References given in the presentation

C-DAC hyPACK-2013

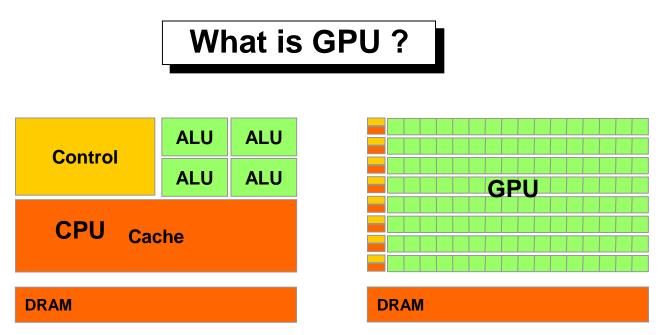

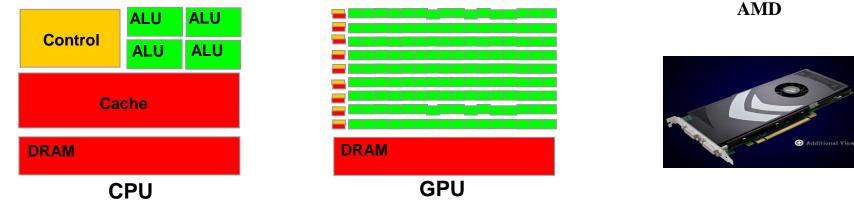

- The GPU is specialized for compute-intensive, highly data parallel computation (exactly what graphics rendering is about)

- So, more transistors can be devoted to data processing rather than data caching and flow control

- Data-parallel portions of an application are executed on the device as kernels which run in parallel on many threads

- ✤ GPU threads are extremely lightweight

- ✤ GPU needs 1000s of threads for full efficiency

- Graphics Processing Unit

- GPU also occasionally called visual processing unit or VPU

- It's a dedicated graphics rendering device for a personal computer, workstation, or game console.

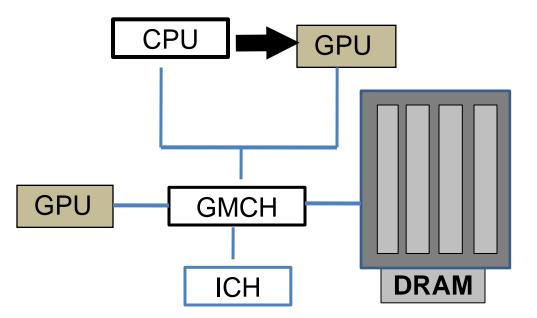

- ✤ GPU is viewed as compute device that :

- Is a coprocessor to CPU or host machine

- Has its own DRAM (on the device)

- Runs many threads in parallel

- Thus GPU is dedicated super-threaded, massively data parallel co-processor

# GPGPU

- Look at GPU as a fast SIMD processor

- It is a specialized processor, so not all programs can be run

- Example computational programs FFT,

- Cryptography, Ray Tracing, Segmentation and even sound processing!

**Source :** References given in the presentation

# History

- Dealing complex with Graphics API

- Sequential Flow of Execution

- LimitedCommunication

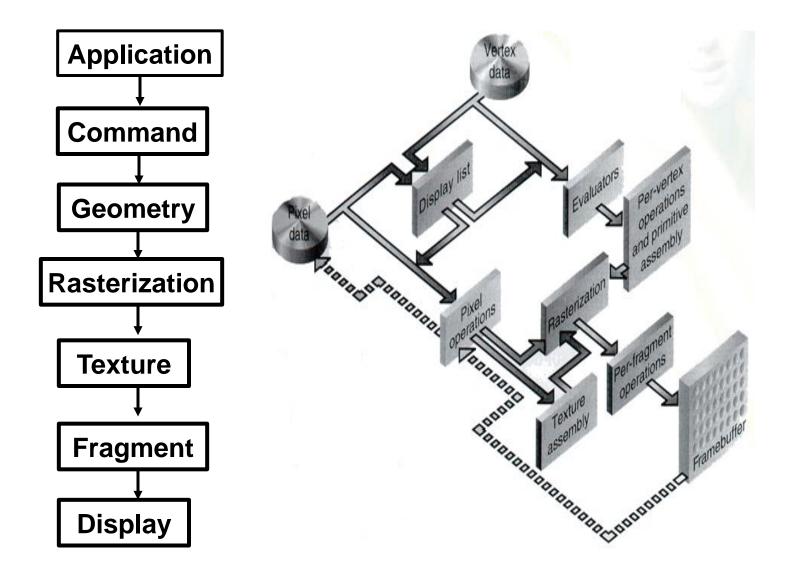

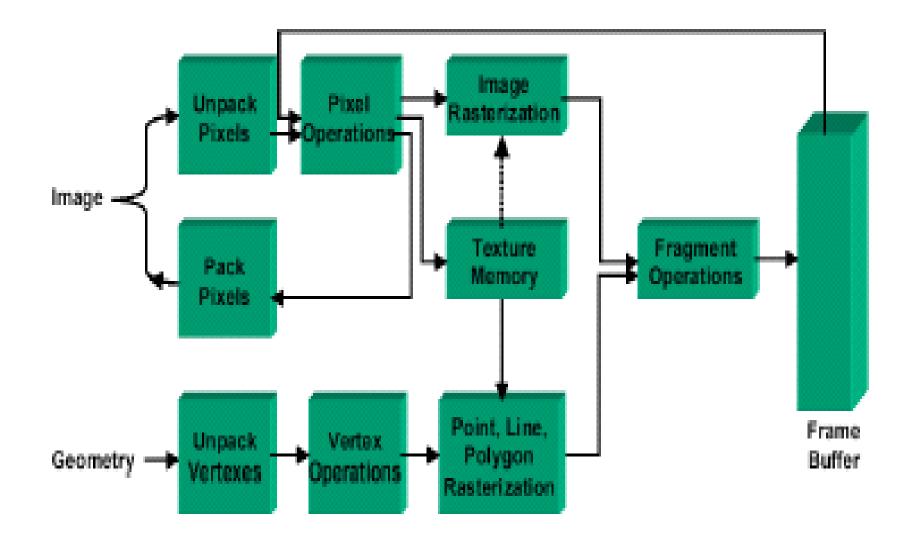

## The Graphics pipeline

#### 3D Graphics Software Interfaces OpenGL (v2.0 as of now)

- Low level

- Specification not an API

- Crossplatform implementations

- Popular with some games

- ✤ A simple seq of opengl instr (in C) glClearColor(0.0,0.0,0.0,0.0); glClear(GL\_COLOR\_BUFFER\_BIT); glColor3f(1.0,1.0,1.0); glOrtho(0.0,1.0,0.0,1.0,-1.0,1.0); glBegin(GL\_POLYGON); glVertex(0.25,0.25,0.0); glVertex(0.75,0.25,0.0); glVertex(0.75,0.75,0.0); glVertex(0.25,0.75,0.0); glEnd();

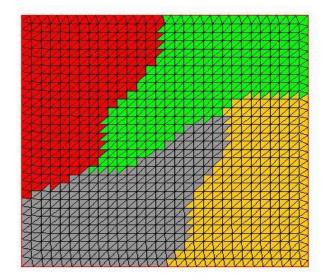

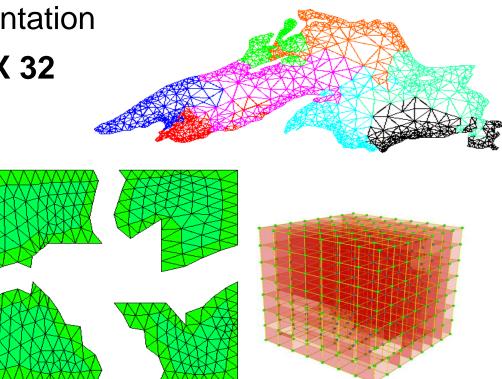

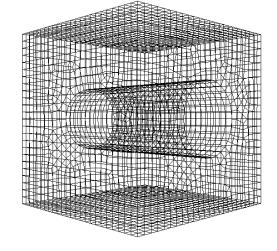

#### **Geometry Processing**

Self intersections

Algebraic Geometry

Dynamic silhouette refinement

Preparation of FEM grids

Source : References

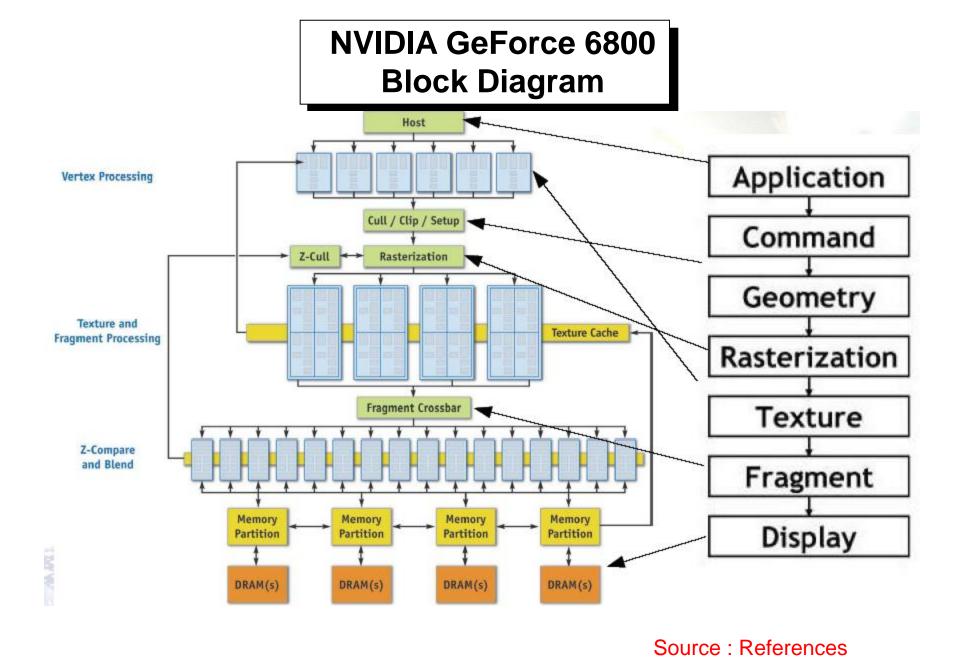

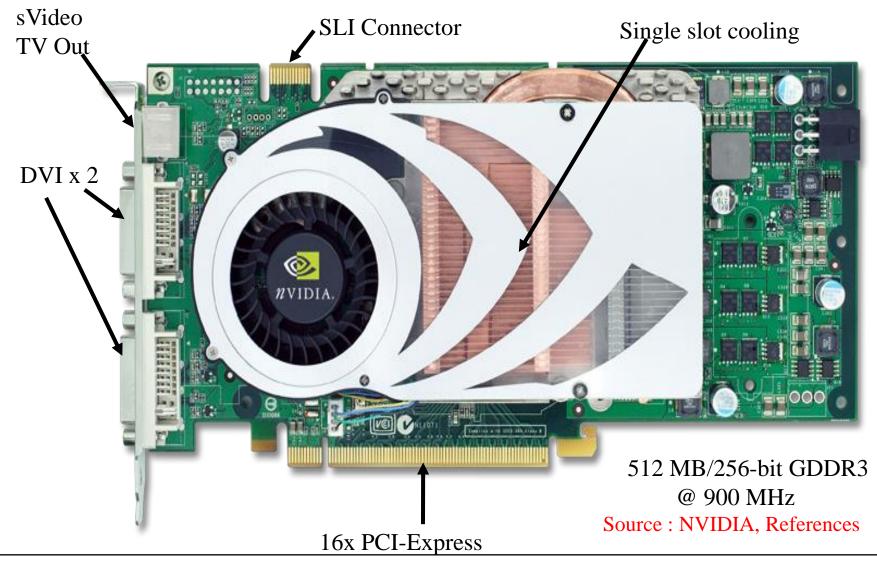

#### NVIDIA GeForce 6800 General Info

- Impressive performance stats

- ➢ 600 Million vertices/s

- ➢ 6.4 billion texels/s

- 12.8 billion pixels/s rendering z/stencil only

- ➢ 64 pixels per clock cycle early z-cull (reject rate)

- Riva series (1st DirectX compatible)

- Riva 128, Riva TNT, Riva TNT2

- ✤ GeForce Series

- GeForce 256, GeForce 3 (DirectX 8), GeForce FX, GeForce 6 series

#### Source : References

**NVIDIA GeForce 6800**

C-DAC hyPACK-2013

Heat

Basics of GPU Based Programming

#### GPU from comp arch perspective Processing units

- Focus on Floating point math

- fp32 and fp16 precision support for intermediate calculations

- 6 four-wide fp32 vector MADs/clock in shaders and 1 scalar multifunction op

- I6 four-wide fp32 vector MADs/clock in frag-proc plus 16 four-wide fp32 MULs

- Dedicated fp16 normalization hardware

Source : References

#### GPU from comp arch perspective Memory

- Use dedicated but standard memory architectures (eg DRAM)

- Multiple small independent memory partitions for improved latency

- Memory used to store buffers and optionally textures

- In low-end system (Intel 855GM) system memory is shared as the Graphics memory

#### GPU from comp arch perspective Memory

- GPU interfaces with the CPU using fast buses like AGP and PCI Express

- Port speeds

- PCI express upto 8GB/sec (4 + 4)

- Practically upto (3.2 + 3.2)

- AGP upto 2 GB/sec (for 8x AGP)

Such bus speeds are important because textures and vertex data needs to come from CPU to GPU (after that it's the internal GPU bandwidth that matters)

**Source :** References given in the presentation

#### GPU from comp arch perspective Memory

#### Texture caches (2 level)

- Shared between vertex procs and fragment procs

- Cache processed/filtered textures

- Vertex caches

- cache processed and unprocessed vertexes

- improve computation and fetch performance

- Z and buffer cache and write queues

#### 3D Graphics Software Interfaces Direct 3D (v9.0 as of now)

✤ High level

- ✤ 3D API part of DirectX

- Very popular in the gaming industry

- Microsoft platforms only

#### **Source :** References given in the presentation

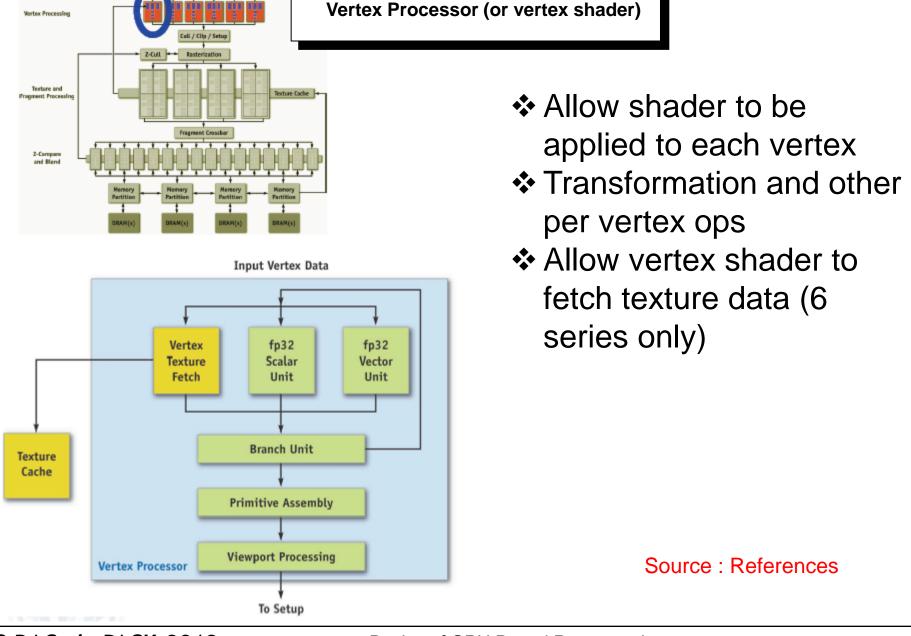

#### **Traditional OpenGL Pipeline**

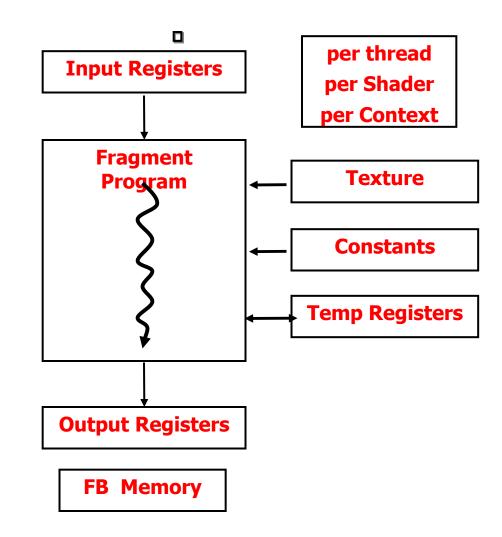

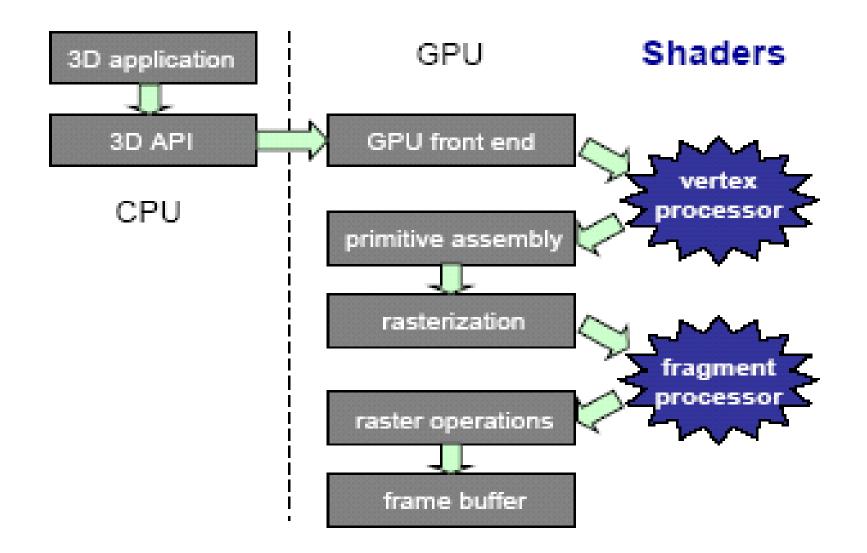

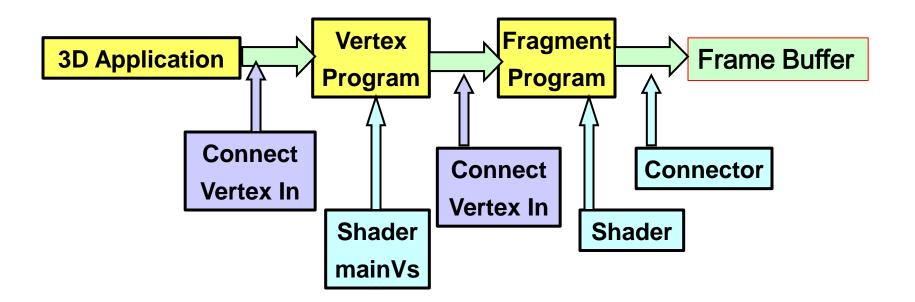

#### Programmable Pipeline

- Most parts of the rendering pipeline can be programmed

- Shading programs to change hardware behavior

- Transform and lighting: vertex shaders / vertex programs

- Fragment processing: pixel shaders / fragment programs

- History: from fixed-function pipeline to configurable pipeline

- Steps towards programmability

#### Programmable Pipeline

#### **GPU** - Issues

How are vertex and pixel shaders specified?

- Low-level, assembler-like

- High-level language

- Data flow between components

- Per-vertex data (for vertex shader)

- Per-fragment data (for pixel shader)

- Uniform (constant) data: e.g. modelview matrix, material parameters

#### **GPU Overview**

- Rendering pipeline on current GPUs

- Low-level languages

- Vertex programming

- Fragment programming

- High-level shading languages

#### What Are Low-Level APIs?

#### Similarity to assembler

- Close to hardware functionality

- Input: vertex/fragment attributes

- Output: new vertex/fragment attributes

- Sequence of instructions on registers

- Very limited control flow (if any)

- Platform-dependent BUT: there is convergence

#### What Are Low-Level APIs?

- Current low-level APIs:

- OpenGL extensions: GL\_ARB\_vertex\_program,

- GL\_ARB\_fragment\_program

DirectX 9: Vertex Shader 2.0, Pixel Shader 2.0

- Older low-level APIs:

- DirectX 8.x: Vertex Shader 1.x, Pixel Shader 1.x

- OpenGL extensions: GL\_ATI\_fragment\_shader, GL\_NV\_vertex\_program, ...

#### **Source :** References given in the presentation

#### Why Use Low-Level APIs?

- Low-level APIs offer best performance & functionality

- Help to understand the graphics hardware (ATI's r300, NVIDIA's nv30, …)

- ✤ Help to understand high-level APIs (Cg, HLSL, …)

- Much easier than directly specifying configurable graphics pipeline (e.g. register combiners)

#### **Applications Vertex Programming**

- Customized computation of vertex attributes

- Computation of anything that can be interpolated linearly between vertices

- Limitations:

- Vertices can neither be generated nor destroyed

- No information about topology or ordering of vertices is available

### OPEN\_GL GL\_ARB\_vertex\_program

Circumvents the traditional vertex pipeline

- What is replaced by a vertex program?

- Vertex transformations

- Vertex weighting/blending

- Normal transformations

- Color material

- Per-vertex lighting

- Texture coordinate generation

- Texture matrix transformations

- Per-vertex point size computations

- Per-vertex fog coordinate computations

- Client-defined clip planes

#### OPEN\_GL GL\_ARB\_vertex\_program

#### What is not replaced?

- Clipping to the view frustum

- Perspective divide (division by w)

- Viewport transformation

- Depth range transformation

- Front and back color selection

- Clamping colors

- Primitive assembly and per-fragment operations

- Evaluators

#### DirectX 9: Vertex Shader 2.0

- Vertex Shader 2.0 introduced in DirectX 9.0

- Similar functionality and limitations as GL\_ARB\_vertex\_program

- Similar registers and syntax

- Additional functionality: static flow control

- Control of flow determined by constants (not by pervertex attributes)

- Conditional blocks, repetition, subroutines

**Source :** References given in the presentation

#### **Applications for Fragment Programming**

- Customized computation of fragment attributes

- Computation of anything that should be computed per pixel

- Limitations:

- Fragments cannot be generated

- Position of fragments cannot be changed

- > No information about geometric primitive is available

## OPEN\_GL\_ARB\_fragment\_program

- Circumvents the traditional fragment pipeline

- What is replaced by a pixel program?

- Texturing

- Color sum

- ➢ Fog

for the rasterization of points, lines, polygons, pixel rectangles, and bitmaps

- What is not replaced?

- Fragment tests (alpha, stencil, and depth tests)

- Blending

#### **GPU Overview**

Rendering pipeline on current GPUs

Low-level languages

- Vertex programming

- Fragment programming

High-level shading languages

#### **High-Level Shading Languages**

- ✤ Why?

- Avoids programming, debugging, and maintenance of long assembly shaders

- Easy to read

- Easier to modify existing shaders

- Automatic code optimization

- Wide range of platforms

- Shaders often inspired RenderMan shading language

#### **Source :** References given in the presentation

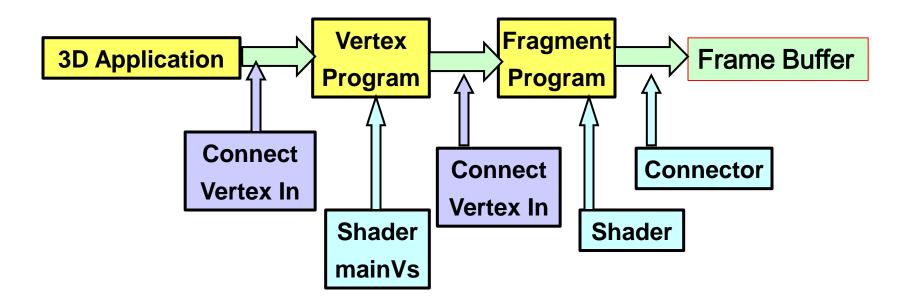

#### Data Flow through Pipeline

- Vertex shader program

- Fragment shader program

- Connectors

#### High-Level Shading Languages

- ✤ Cg➢ "C for Graphics"

- > By NVIDIA

- ✤ HLSL

- High-level shading language"

- Part of DirectX 9 (Microsoft)

- OpenGL 2.0 Shading Language

- Proposal by 3D Labs

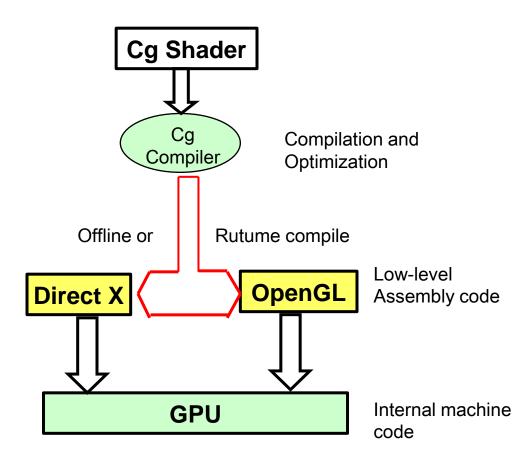

## GPU - Cg

- Typical concepts for a high-level shading language

- Language is (almost) identical to DirectX HLSL

- Syntax, operators, functions from C/C++

- Conditionals and flow control

- Backends according to hardware profiles

- Support for GPU-specific features (compare to low-level)

- Vector and matrix operations

- Hardware data types for maximum performance

- Access to GPU functions: mul, sqrt, dot, …

- Mathematical functions for graphics, e.g. reflect

- Profiles for particular hardware feature sets

## Workflow in Cg

#### Phong Shading in Cg: Vertex Shader

- First part of pipeline

- Connectors: what kind of data is transferred to/from vertex program?

- Actual vertex shader

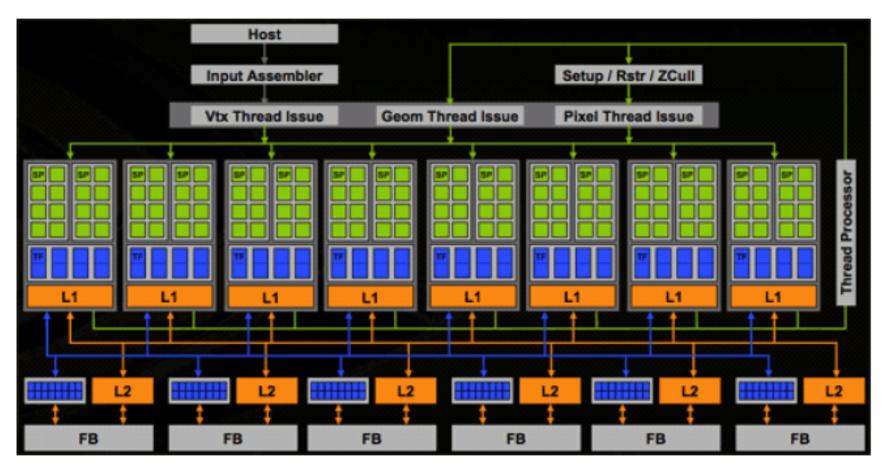

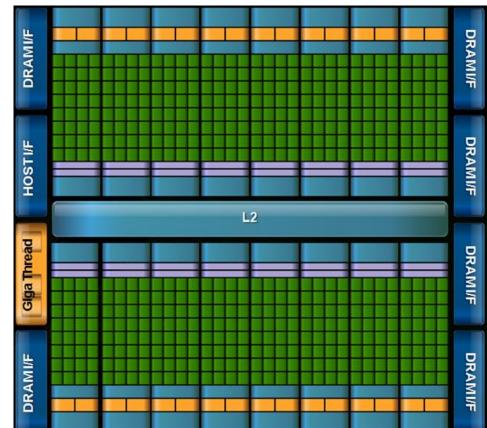

#### NVIDIA G80 Block Diagram

- Very little of this is graphic specic

- ...but, assumes threads are independent

#### Hyper "Core" Computers

Speculation about the computer of the next decade:

- 10s of CPU cores

- Use for scheduling

- Use for \irregular" part of problem

- Maybe higher precision (correction steps)

- 100s of GPU cores

- Use for \regular" part of problem

- NUMA (Non-Uniform Memory Access) for both

- Programming languages must expose this

- Runtime systems?

- Always out-of-(some)-core

- Clusters of these?

- OpenMP/MPI not sufficient

#### Limitations of GPUs

If the GPU is so great, why are we still using the CPU? You can not simply "port" existing code and algorithms!

- Data-stream mindset required

- Parallel algorithms

- New data structures (dynamic data structures are troublesome)

- Not suitable to all problems

- Pointer chasing impossible or inecient

- Recursion

- Debugging is hard

- Hardware is designed without debug bus

- Driver is closed

- Huge performance clis

- No standard API

- More about this later...

#### **GPU Programming**

GPUs have traditionally been closed architectures.

- Must program them through closed-source graphics driver

- Driver is like an OS (threads, scheduling, protected memory)

- OpenGL/DirectX are standard, but

- Designed for graphics, not general purpose computations

- Many revisions of each standard

Now revisions for each HW general

- New revisions for each HW-generation

- Allows for \capabilities"

- Large variations between vendors

- Both vendors now have dedicated GPGPU APIs

- Nvidia CUDA (Compute Unified Device Architecture)

- AMD CTM (Close To Metal) AMD ATI FireStream

- GPGPU version" of hardware as well

# Part-I (B)

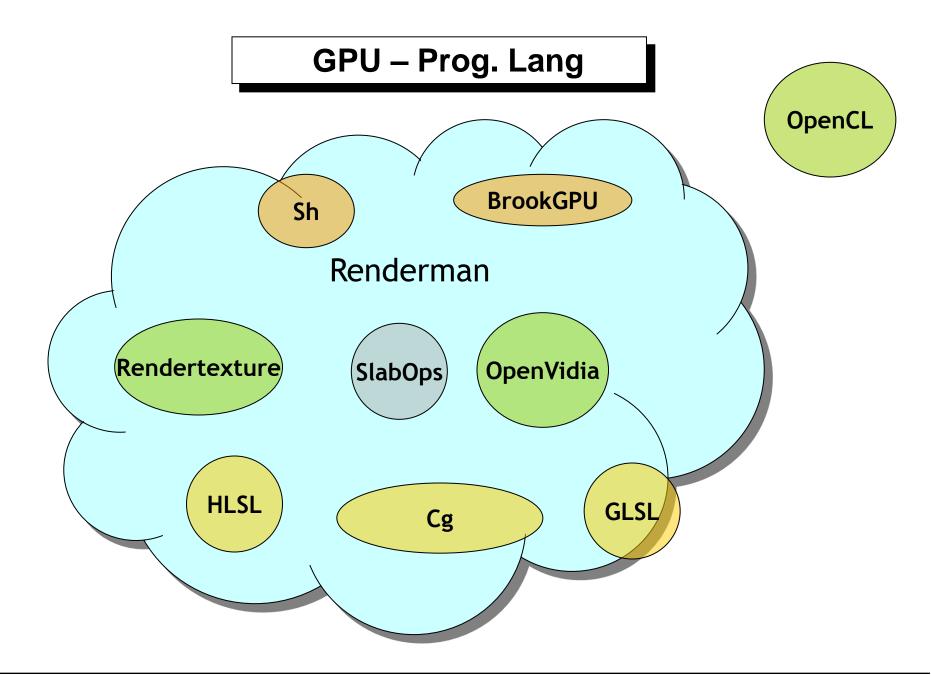

## An Overview of GPU Prog. Languages

Source & Acknowledgements : NVIDIA, AMD, References

C-DAC hyPACK-2013

#### **GPU - Some History**

- Cook and Perlin first to develop languages for performing shading calculations

- Perlin computed noise functions procedurally; introduced control constructs

- Cook developed idea of *shade trees* @Lucasfilm

- These ideas led to development of Renderman at Pixar (Hanrahan *et al*) in 1988.

- Renderman is STILL shader language of choice for high quality rendering !

- Languages intended for offline rendering; no interactivity, but high quality.

#### **GPU - Some History**

- After RenderMan, independent efforts to develop high level shading languages at SGI (ISL), Stanford (RTSL).

- ISL targeted fixed-function pipeline and SGI cards (remember compiler from previous lecture): goal was to map a RenderMan-like language to OpenGL

- RTSL took similar approach with programmable pipeline and PC cards (recall compiler from previous lecture)

- **♦** RTSL morphed into **Cg**.

#### **GPU - Some History**

- Cg was pushed by NVIDIA as a platform-neutral, card-neutral programming environment.

- In practice, Cg tends to work better on NVIDIA cards (better demos, special features etc).

- ATI made brief attempt at competition with Ashli/RenderMonkey.

- HLSL was pushed by Microsoft as a DirectXspecific alternative.

- In general, HLSL has better integration with the DirectX framework, unlike Cg with OpenGL/DirectX.

#### GPU – Level 1: Better Than Assembly ?

## **Overview** –

## C-like vertex, Cg, HLSL, GLSL, Data Types, Shaders, Compilation

#### GPU Lang. - Prog.: C-like vertex and fragment code

- Languages are specified in a C-like syntax.

- The user writes explicit vertex and fragment programs.

- Code compiled down into pseudo-assembly

- this is a source-to-source compilation: no machine code is generated.

- Knowledge of the pipeline is essential

- Passing array = binding texture

- Start program = render a quad

- Need to set transformation parameters

- Buffer management a pain

## GPU Lang. - Prog.: Cg

- Platform neutral, architecture "neutral" shading language developed by NVIDIA.

- One of the first GPGPU languages used widely.

- Because Cg is platform-neutral, many of the other GPGPU issues are not addressed

- managing pbuffers

- rendering to textures

- handling vertex buffers

"As we started out with Cg it was a great boost to getting programmers used to working with programmable GPUs. Now Microsoft has made a major commitment and in the long term we don't really want to be in the programming language busies"

> David Kirk, NVIDIA

## GPU Lang. - Prog.: HLSL

- Developed by Microsoft; tight coupling with DirectX

- Because of this tight coupling, many things are easier (no RenderTexture needed !)

- Xbox programming with DirectX/HLSL (XNA)

But...

Cell processor will use OpenGL/Cg

## GPU Lang. - Prog.: GLSL

- GLSL is the latest shader language, developed by 3DLabs in conjunction with the OpenGL ARB, specific to OpenGL.

- Requires OpenGL 2.0

- NVIDIA doesn't yet have drivers for OpenGL 2.0 !! Demos (appear to be) emulated in software

- ATI appears to have native GL 2.0 support and thus support for GLSL.

Multiplicity of languages likely to continue

#### GPU Lang. - Prog.: Datatypes

- Scalars: float/integer/boolean

- Scalars can have 32 or 16 bit precision (ATI supports 24 bit, GLSL has 16 bit integers)

- vector: 3 or 4 scalar components.

- Arrays (but only fixed size)

- Limited floating point support; no underflow/overflow for integer arithmetic

- No bit operations

- Matrix data types

- Texture data type

- power-of-two issues appear to be resolved in GLSL

- different types for 1D, 2D, 3D, cubemaps.

#### GPU Lang. - Prog.: DatatBinding

Data Binding modes:

- uniform: the parameter is fixed over a glBegin()glEnd() call.

- varying: interpolated data sent to the fragment program (like pixel color, texture coordinates, etc)

- Attribute: per-vertex data sent to the GPU from the CPU (vertex coordinates, texture coordinates, normals, etc).

- Data direction:

- in: data sent into the program (vertex coordinates)

- out: data sent out of the program (depth)

- inout: both of the above (color)

#### **GPU Lang. - Prog.: Operations And Control Flow**

- Usual arithmetic and special purpose algebraic ops (trigonometry, interpolation, discrete derivatives, etc)

- ✤No integer mod...

- ✤ for-loops, while-do loops, if-then-else statements.

- **discard** allows you to kill a fragment and end processing.

- Recursive function calls are unsupported, but simple function calls are allowed

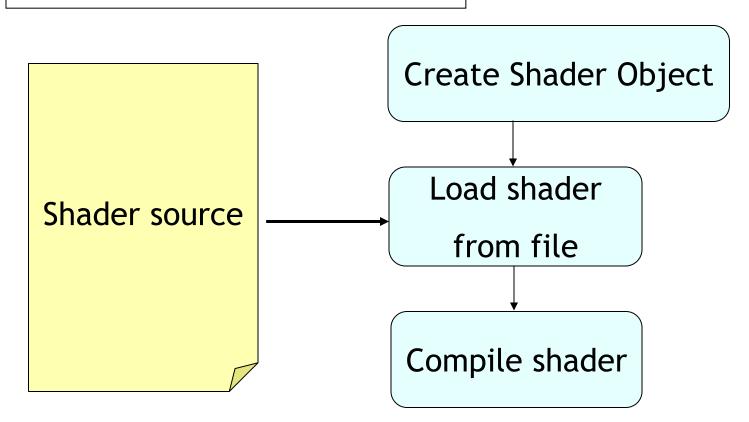

- Always one "main" function that starts the program, like C.

- This is the most painful part of working with shaders.

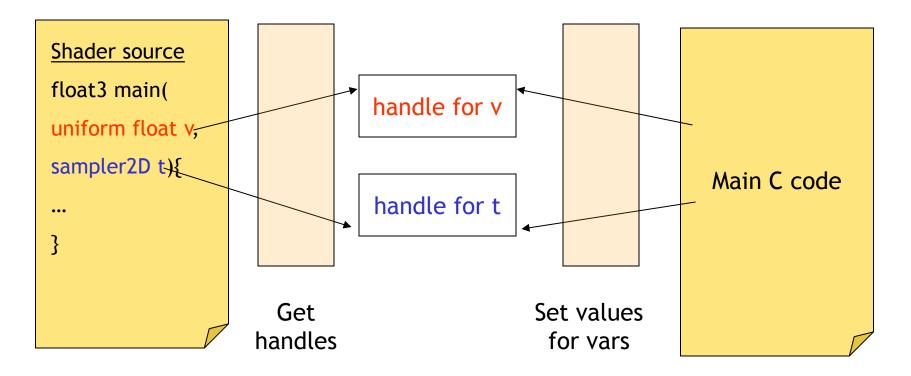

- All three languages provide a "runtime" to load shaders, link data with shader variables, enable and disable programs.

- Cg and HLSL compile shader code down to assembly ("source-to-source").

- GLSL relies on the graphics vendor to provide a compiler directly to GPU machine code, so no intermediate step takes place.

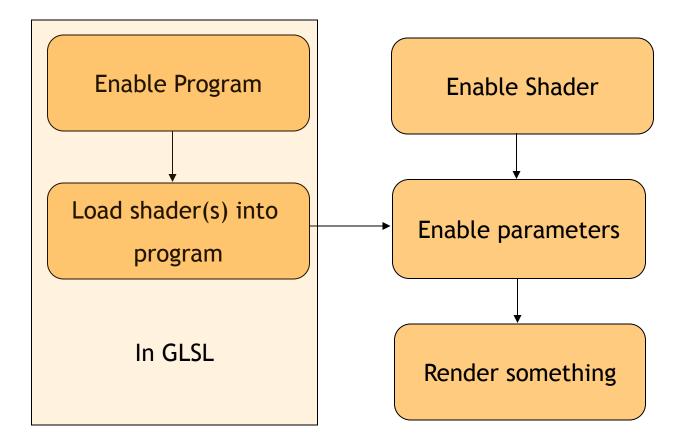

## Step 1: Load the shader

## **Step 2: Bind Variables**

## **Step 3: Run the Shaders**

#### **GPU Lang.-Prog.: Direct Compilation**

- Cg code can be compiled to fragment code for different platforms (directx, nvidia, arbfp)

- HLSL compiles directly to direct

- ♦ GLSL compiles natively.

- It is often the case that inspecting the Cg compiler output reveals bugs, shows inefficiencies etc that can be fixed by writing assembly code (like writing asm routines in C)

- In GLSL you can't do this because the code is compiled natively: you have to trust the vendor compiler !

#### GPU Lang.-Prog.: Overview

- Shading languages like Cg, HLSL, GLSL are ways of approaching Renderman but using the GPU.

- These will never be the most convenient approach for general purpose GPU programming

- But they will probably yield the most efficient code

- you either need an HLL and great compilers

- or you suffer and program in these.

#### GPU – Lang. Prog.; Wrapper libraries

- Writing code that works cross-platform, with all extensions, is hard.

- Wrappers take care of the low-level issues, use the right commands for the right platform, etc.

## **\*** Render Texture:

- Handles offscreen buffers and render-to-texture cleanly

- works in both windows and linux (only for OpenGL though)

- de facto class of choice for all Cg programming (use Cg for the code, and **RenderTexture** for texture management).

### **GPU – Lang. Prog.**; **OpenVidia**

- Video and image processing library developed at University of Toronto.

- Contains a collection of fragment programs for basic vision tasks (edge detection, corner tracking, object tracking, video compositing, etc)

- Provides a high level API for invoking these functions.

- Works with Cg and OpenGL, only on linux (for now)

- Level of transparency is low: you still need to set up GLUT, and allocate buffers, but the details are somewhat masked)

#### GPU – Lang. Prog. : OpenVidia Example

- Create processing object:

- d=new FragPipeDisplay(<parameters>);

- Create image filter

- filter1 = new GenericFilter(...,<cgprogram>);

- ✤ Make some buffers for temporary results:

- d->init\_texture(0, 320, 240, foo);

- d->init\_texture4f(1, 320, 240, foo);

- ✤ Apply filter to buffer, store in output buffer

- d->applyFilter(filter1, 0,1);

#### GPU – Lang. Prog. : High Level C-like languages

- Main goal is to hide details of the runtime and distill the essence of the computation.

- These languages exploit the stream aspect of GPUs explicitly

- They differ from libraries by being general purpose.

- They can target different backends (including the CPU)

- Either embed as C++ code (Sh) or come with an associated compiler (Brook) to compile a C-like language.

### GPU Lang. Prog. : High Level C-like languages : Sh

- Open-source code developed by group led by Michael McCool at Waterloo

- Technical term is 'metaprogramming'

- Code is embedded inside C++; **no** extra compile tools are necessary.

- Sh uses a *staged compiler*: parts of code are compiled when C++ code is compiled, and the rest (with certain optimizations) is compiled at runtime.

- Has a very similar flavor to functional programming

- Parameter passing into streams is seamless, and resource constraints are managed by *virtualization*.

#### GPU Lang. Prog. : High Level C-like languages :Sh And more ..... DirectX

- All kinds of other functions to extract data from streams and textures.

- Lots of useful 'primitive' streams like passthru programs and generic vertex/fragment programs, as well as specialized lighting shaders.

- Sh is closely bound to OpenGL; you can specify all usual OpenGL calls, and Sh is invoked as usual via a display() routine.

- Plan is to have DirectX binding ready shortly (this may be already be in)

- Because of the multiple backends, you can debug a shader on the CPU backend first, and then test it on the GPU.

#### GPU Lang. Prog. : High Level C-like languages Brook GPU

- Open-source code developed by Ian Buck and others at Stanford.

- Intended as a pure stream programming language with multiple backends.

- Is not embedded in C code; uses its own compiler (brcc) that generates C code from a .br file.

- **Workflow:**

- Write Brook program (.br)

- Compile Brook program to C (brcc)

- Compile C code (gcc/VC)

# GPU Lang. Prog. : High Level C-like languages Brook GPU

- Designed for general-purpose computing (this is primary difference in focus from Sh)

- You will almost never use any graphics commands in Brook.

- Basic data type is the stream.

- Types of functions:

# GPU Lang. Prog. : High Level C-like languages Brook GPU

- Types of functions:

- Kernel: takes one or more input streams and produces an output stream.

- Reduce: takes input streams and reduces them to scalars (or smaller output streams)

- Scatter:  $a[o_i] = s_i$ . Send stream data to array, putting values in different locations.

- Gather: Inverse of scatter operation.  $s_i = a[o_i]$ .

• Support of all operations are required ... check.

# GPU Lang. Prog. : High Level C-like languages Sh Vs Brook GPU

- Brook is more general: you don't need to know graphics to run it.

- <sup>©</sup> Very good for prototyping

- You need to rely on compiler being good.

- Many special GPU features cannot be expressed cleanly.

- Sh allows better control over mapping to hardware.

- Embeds in C++; no extra compilation phase necessary.

- Lots of behind-the-scenes

work to get virtualization: is

there a performance hit ?

- Still requires some understanding of graphics.

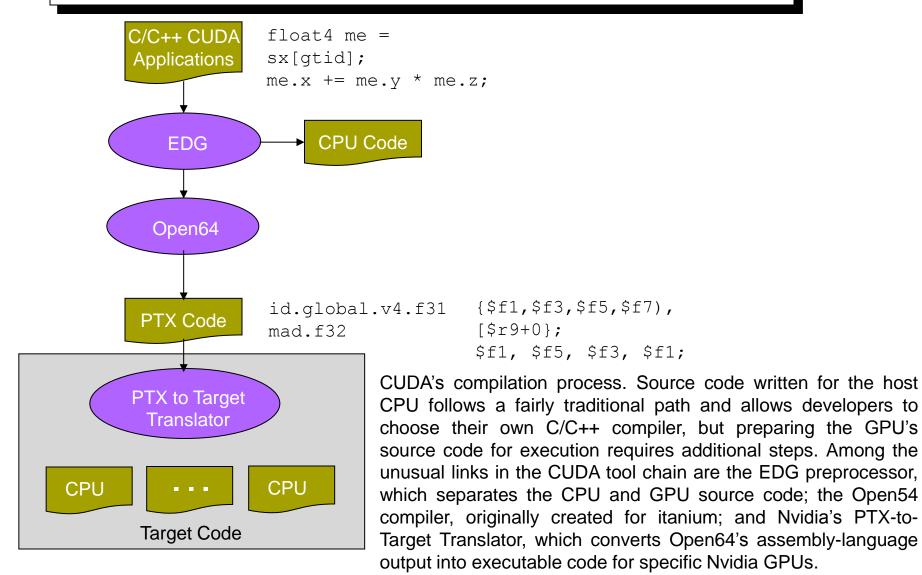

# **NVIDIA CUDA (Compute Unified Device Architecture)**

C-like API for programming newer Nvidia GPUs

- Computation kernels are written in C

- Compiles with dedicated compiler, nvcc

- Kernels are executed as threads, threads organized into blocks

- Programmer decides #threads, #threads/block, and mem/block

- Exposes different kinds of memory

- Thread-local (register)

- Shared per block

- Global (not cached, write everywhere)

- Texture (cached read only memory)

- Constant(cached read only memory)

- Some synchronization primitives

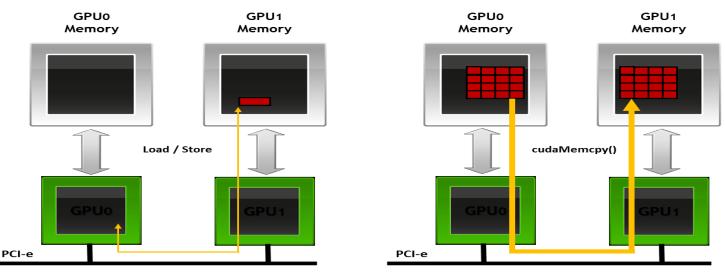

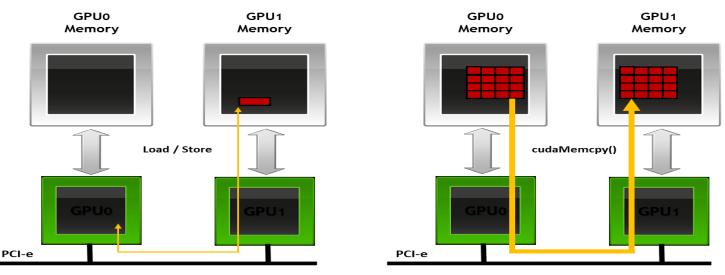

- cudaMalloc, cudaMemcpy for allocating and copying memory

# GPU Lang. Prog. : High Level C-like languages The Big Picture

- The advent of Cg, and then Brook/Sh signified a huge increase in the number of GPU apps. Having good programming tools is worth a lot !

- The tools are still somewhat immature; almost nonexistent debuggers and optimizers, and only one GPU simulator (Sm).

- I shouldn't have to worry about the correct parameters to pass when setting up a texture for use as a buffer: we need better wrappers.

# GPU Lang. Prog. : High Level C-like languages The Big Picture

Compiler efforts are lagging application development: more work is needed to allow for high level language development without compromising performance.

In order to do this, we need to study stream programming. Maybe draw ideas from the functional programming world ?

Libraries are probably the way forward for now.

# Hyper "Core" Computers

Speculation about the computer of the next decade:

- 10s of CPU cores

- Use for scheduling

- Use for \irregular" part of problem

- Maybe higher precision (correction steps)

- 100s of GPU cores

- Use for \regular" part of problem

- NUMA (Non-Uniform Memory Access) for both

- Programming languages must expose this

- Runtime systems?

- Always out-of-(some)-core

- Clusters of these?

- OpenMP/MPI not sufficient

# Limitations of GPUs

If the GPU is so great, why are we still using the CPU? You can not simply "port" existing code and algorithms!

- Data-stream mindset required

- Parallel algorithms

- New data structures (dynamic data structures are troublesome)

- Not suitable to all problems

- Pointer chasing impossible or inecient

- Recursion

- Debugging is hard

- Hardware is designed without debug bus

- Driver is closed

- Huge performance clis

- No standard API

- More about this later...

# **GPU Programming**

GPUs have traditionally been closed architectures.

- Must program them through closed-source graphics driver

- Driver is like an OS (threads, scheduling, protected memory)

- OpenGL/DirectX are standard, but

- Designed for graphics, not general purpose computations

- Many revisions of each standard

Now revisions for each HW general

- New revisions for each HW-generation

- Allows for \capabilities"

- Large variations between vendors

- Both vendors now have dedicated GPGPU APIs

- Nvidia CUDA (Compute Unified Device Architecture)

- AMD CTM (Close To Metal) AMD ATI FireStream

- GPGPU version" of hardware as well

Conclusions

GPU Programming Language

GPU Programming – OpenGL, DirectX, NVIDIA (CUDA), AMD (Brook+)

✤ OPECG-2009 -Hands-on session : Examples

# This page is intentionally kept blank

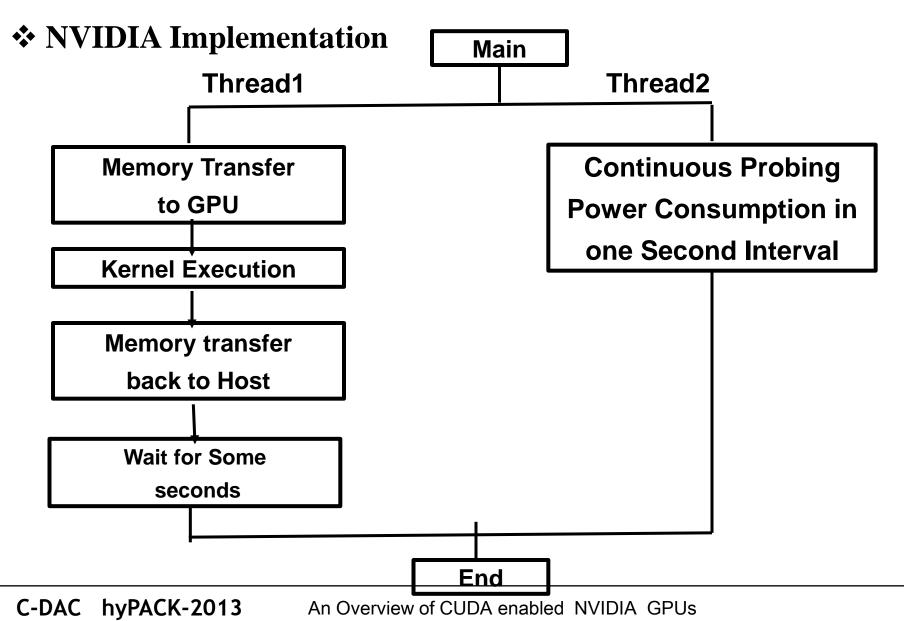

# Part-II(A)

# An Overview of CUDA enabled NVIDIA GPUs

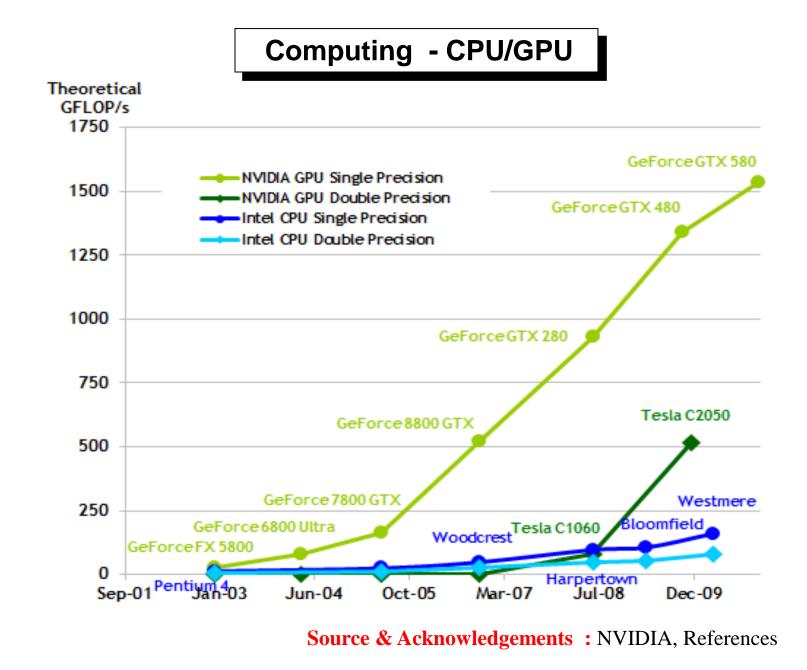

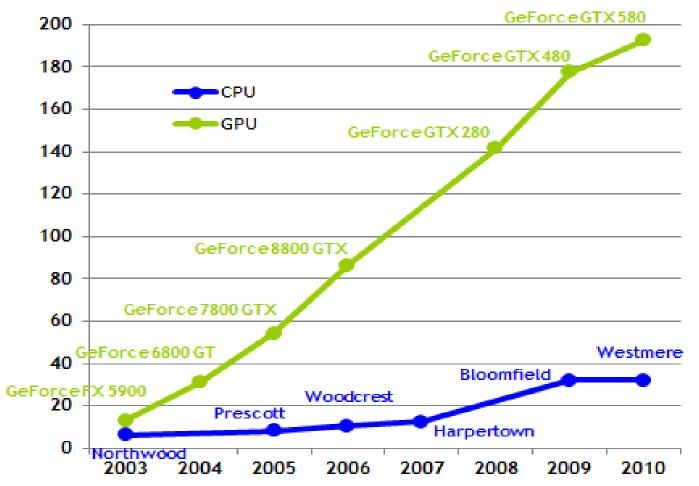

# Computing - CPU/GPU

Theoretical GB/s

Floating-Point Operations per Second and Memory Bandwidth for the CPU and GPU

#### Why Are GPUs So Fast?

- GPU originally specialized for math-intensive, highly parallel computation

- So, more transistors can be devoted to data processing rather than data caching and flow control

NVIDIA

- Commodity industry: provides economies of scale

- Competitive industry: fuels innovation

## GPU Computing : Think in Parallel

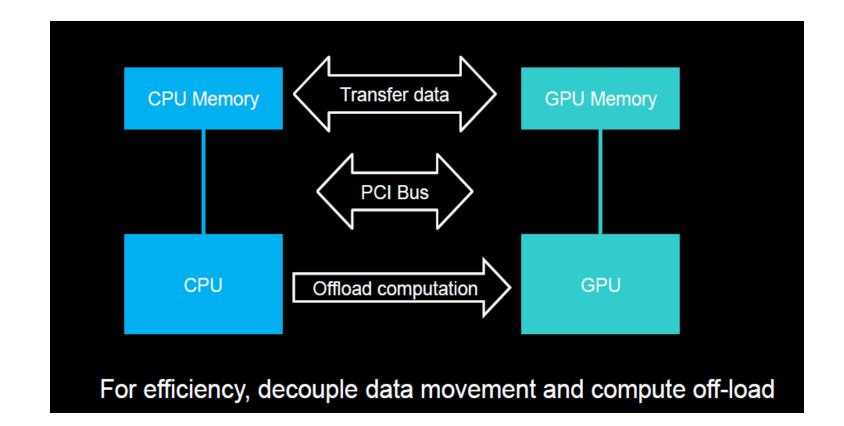

# **Some Design Goals**

- Scale to 100's of cores, 1000's of parallel

- threads

- Let programmers focus on parallel algorithms & Re-writing the Code

- Not on the mechanics of a parallel programming language

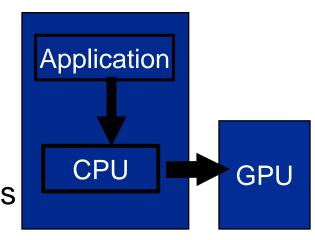

- Enable heterogeneous systems (i.e. CPU + GPU)

- CPU and GPU are separate devices with separate DRAMs

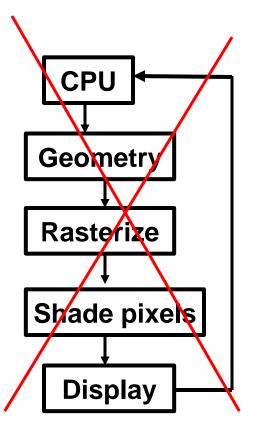

# **Computer Graphics**

Hardware mimicked graphics APIs

It is possible to formulate many problems in this framework

Uses graphics APIs

Classical GPGPU"

DO NOT DO THIS ANYMORE! (Unless for graphics)

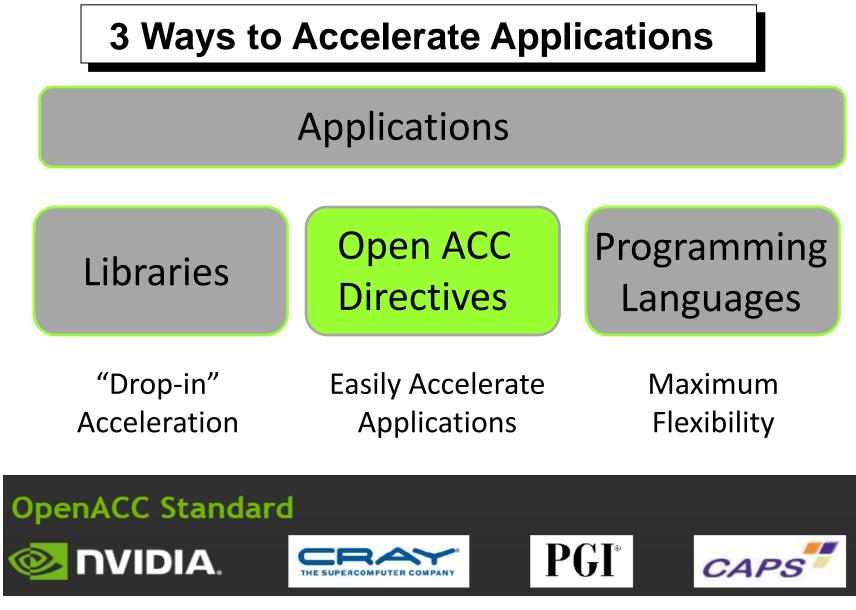

Use GPU Computing with CUDA APIs for Data Parallel Computations .(CUDA = Compute Unified Device Architecture. CUDA is co-designed hardware & software for direct GPU computing)

"OpenCL will enable programmers to easily develop portable applications that maximize the performance on GPU architectures. **GPU Computing : Think in Parallel**

Performance = parallel hardware

scalable parallel program

GPU Computing drives new applications

- Reducing "Time to Discovery"

- 100 x Speedup changes science & research methods

- New applications drive the future of GPUs

- Drives new GPU capabilities

- Drives hunger for more performance

#### **GPU Computing : Think in Parallel**

- Speedups of 8 x to 30x are quite common for certain class of applications

The GPU is a data-parallel processor

- Thousands of parallel threads

- Thousands of data elements to process

- All data processed by the same program

- SPMD computation model

- Contrast with task parallelism and ILP

- Best results when you "Think Data Parallel"

- Design your algorithm for data-parallelism

- Understand parallel algorithmic complexity and efficiency

- Use data-parallel algorithmic primitives as building blocks

**Source & Acknowledgements :** NVIDIA, References

Source : NVIDIA, AMD, References

#### Why Are GPUs So Fast?

- Optimized for structured parallel execution

- Extensive ALU counts & Memory Bandwidth

- Cooperative multi-threading hides latency

- Shared Instructions Resources

- Fixed function units for parallel workloads dispatch

- Extensive exploitations of Locality

- •Performance /(Cost/Watt); Power for Core

- •Structured Parallelism enables more flops less watts

Source : NVIDIA, AMD, References

# **GPU Computing : Optimise Algorithms for the GPU**

- Maximize independent parallelism

- Maximize arithmetic intensity (math/bandwidth)

- Sometimes it's better to recompute than to cache

- GPU spends its translators on ALUs, not memory

- Do more computation on the GPU to avoid costly data transfers

Even low parallelism computations can sometimes be faster than transferring back and forth to host

# **GPU Computing : Use Parallelism Efficiently**

- Partition your computation to keep the GPU multiprocessors equally busy

- Many threads, many thread blocks

- Keep resource usage low enough to support multiple active thread blocks per multiprocessor

- Registers, shared memory

Source : NVIDIA, AMD, References

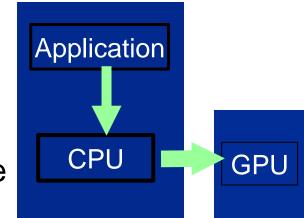

# **GPU Programming : Two Main Challenges**

Application

CPU

GPU Challenges with regard to Scientific Computing

Challenge 1 : Programmability

- Example : Matrix Computations

- To port an existing scientific application to a GPU

- GPU memory exists on the card itself

- Must send matrix array over PCI-Express But

- Send A, B, C to GPU over PCIe

- -Perform GPU-based computations on A,B, C

- Read result C from GPU over PCIe

- The user must focus considerable effort on optimizing performance by manually orchestrating data movement and managing thread level parallelism on GPU.

**GPU**

# **GPU Programming : Two Main Challenges**

#### Challenge 2 : Accuracy

- Example : Non-Scientific Computation Video Games (Frames) (A single bit difference in a rendered pixel in a real-time graphics program may be discarded when generating subsequence frames)

- Past History : Most GPUs support single/double precision, 32 bit /64-bit floating point operation, - all GPUs have necessarily implemented the full IEEE Standard for Binary Floating-Point Arithmetic (IEEE 754)

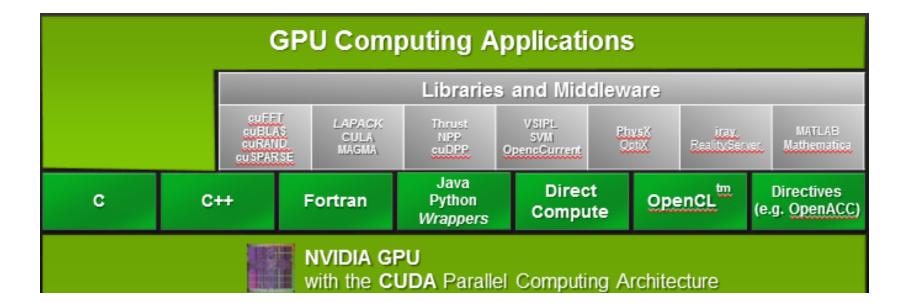

#### **NVIDIA GPU Computing - CUDA Kernels and Threads**

CUDA is Designed to Support Various Languages and Application Programming Interfaces

**NVIDIA - GPU Computing CUDA Kernels and Threads**

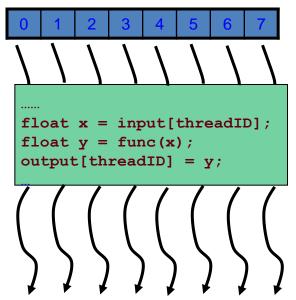

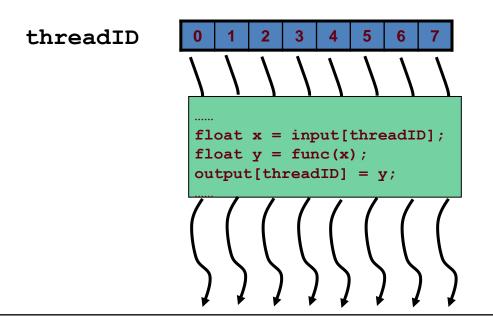

# **Arrays of Parallel Threads**

**\*** A CUDA kernel is executed by an array of threads

- All threads run the same code

- Each thread has an ID that it uses to compute memory addresses and make control decisions

#### **Solution: GPU Computing – NVIDIA CUDA**

- **NEW:** *GPU Computing* with CUDA

- CUDA = Compute Unified Driver Architecture

- Co-designed hardware & software for direct GPU computing

- Hardware: fully general data-parallel architecture

- General thread launch

- Global load-store

- Parallel data cache

- Software: program the GPU in C

- Scalable data-parallel execution/ memory model

- Scalar architecture

- Integers, bit operations

- Single / Double precision C with powerful extensions

- > CUDA 4.0 /CUDA 5.0

# **NVIDA : CUDA - Quick terminology review**

- CUDA is a development platform designed for writing and running general-purpose applications on the *nVIDIA* GPU

- Similar to Graphics applications, CUDA applications can be accelerated by data-parallel computation of millions of *threads.*

- A thread here is an instance of a kernel, namely a program running on the GPU.

- GPU platform can be regarded as a single instruction, multiple data (SIMD) parallel machine rather than graphics hardware

- Keeping **SIMD** in mind, there is no need to understand the graphics pipeline to execute programs on this highly threaded architecture.

#### **CUDA - Quick terminology review**

- Thread: concurrent code and associated state executed on the CUDA device (in parallel with other threads)

- The unit of parallelism in CUDA

- Note difference from CPU threads: creation cost, resource usage, and switching cost of GPU threads is much smaller

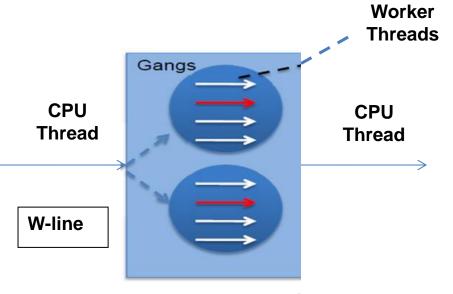

- Warp: a group of threads executed physically in parallel (SIMD)

- Thread Block: a group of threads that are execute together and can share memory on a single multiprocessor

- Grid: a group of thread blocks that execute a single CUDA program logically in parallel

- ✤ Device: GPU Host: CPU

- SM: Multiprocessor

Source : NVIDIA, References

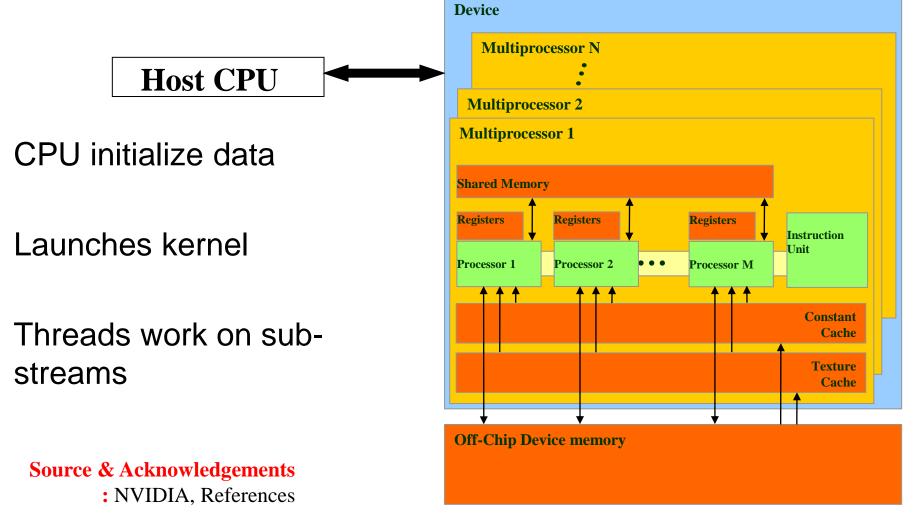

**NVIDA : CUDA – Data Parallelism**

# To a CUDA Developer,

- The computing system consists of a host, which is a traditional central processing unit (CPU) such as Intel, AMD, IBM, Cray multi-core architecture and one more devices, which are massively parallel processors equipped with a large number of arithmetic execution units.

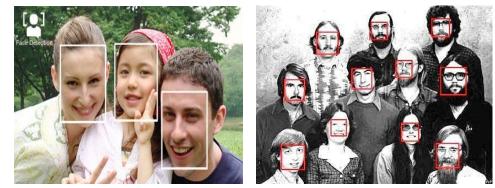

- Computing depends upon the concept of *Data Parallelism* Image Processing, Video Frames, Physics, Aero dynamics, Chemistry, Bio-Informatics

- Regular Computations and Irregular Computations.

#### **NVIDIA GPU Computing - CUDA Kernels and Threads**

- ✤ NEW: GPU Computing with CUDA

- CUDA = Compute Unified Device Architecture

- Co-designed hardware & software for direct GPU computing

- Hardware: fully general data-parallel architecture

- General thread launch; Global load-store

- Parallel data cache

- ✤ Software: program the GPU in C /C++

- Scalable data-parallel execution/ memory model; Single/Double precision

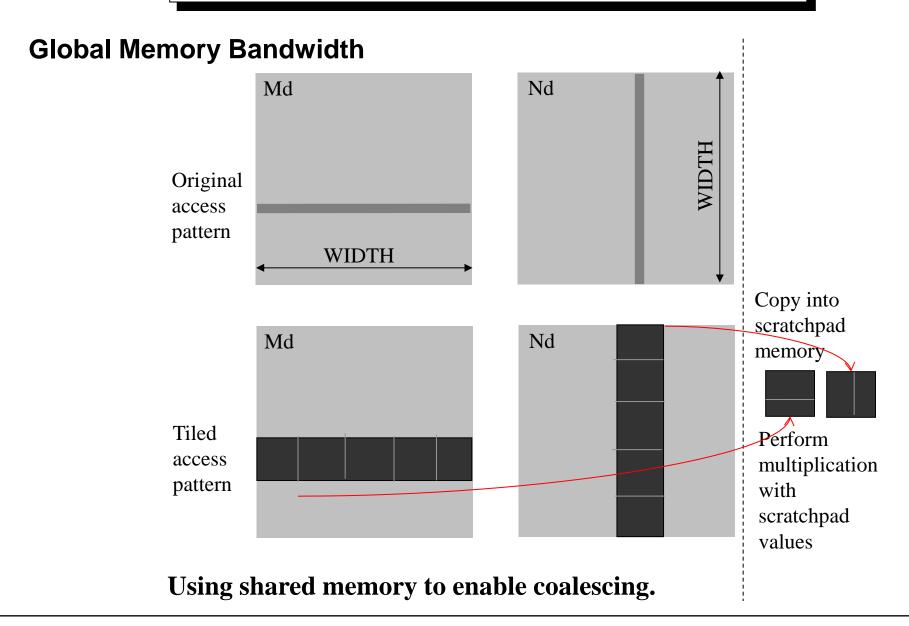

- Hundreds of times faster than global memory

- Use one/ a few threads to load/computer data shared by all thread

Source & Acknowledgements : NVIDIA, References

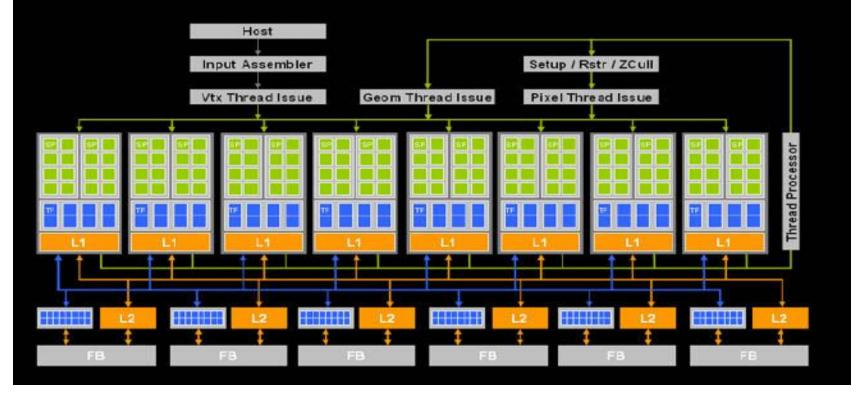

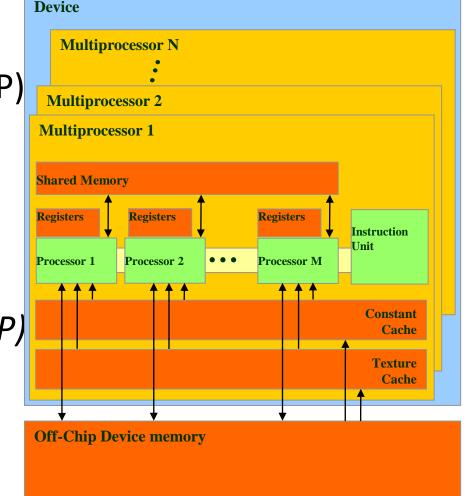

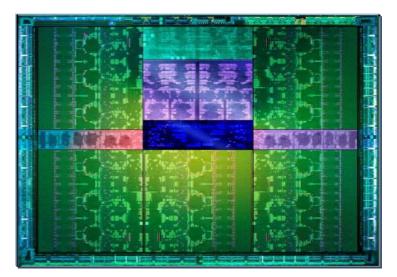

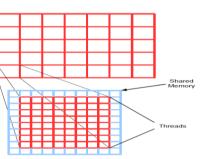

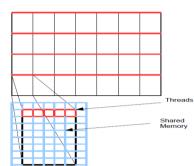

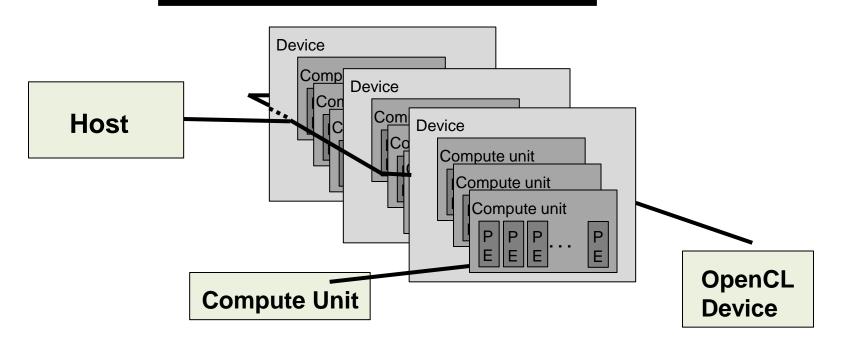

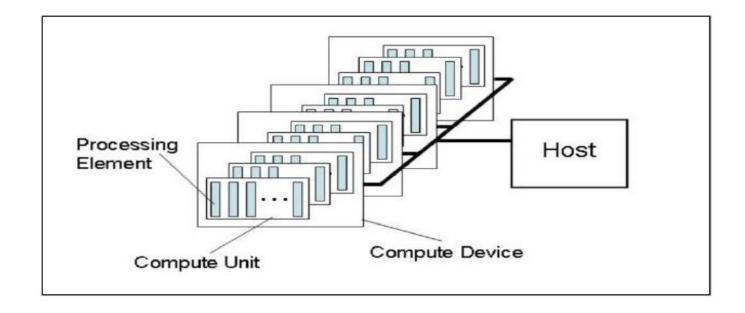

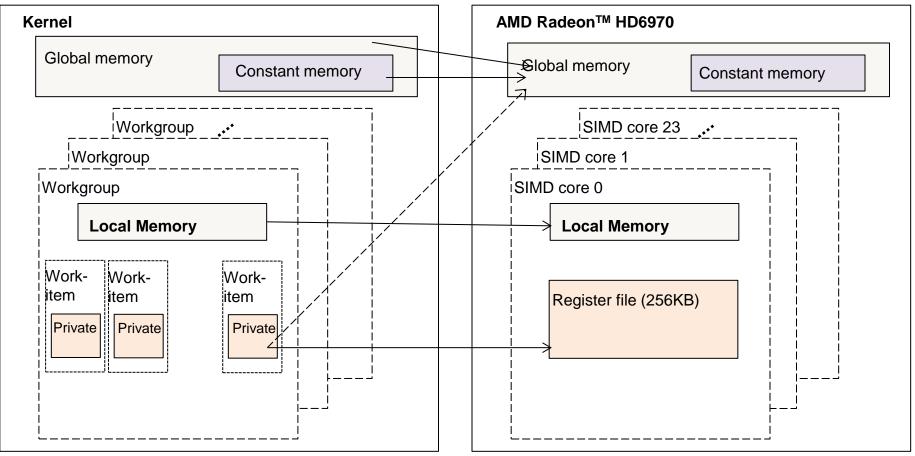

# **GPU : Architecture**

Several multiprocessors (MP), each with:

- several simple cores

- small shared memory

- The threads executing in the same MP must execute the same instruction

- Shared memory must be used to prevent the high latency of the global device memory

# Glance at NVIDIA GPU's

NVIDIA GPU Computing Architecture is a separate HW interface that can be plugged into the desktops / workstations / servers with little effort.

♦ G80 series GPUs /Tesla deliver FEW HUNDRED to TERAFLOPS on compiled parallel C applications

# GeForce 8800 GT Card

C-DAC hyPACK-2013 An Overview of CUDA enabled NVIDIA GPUs

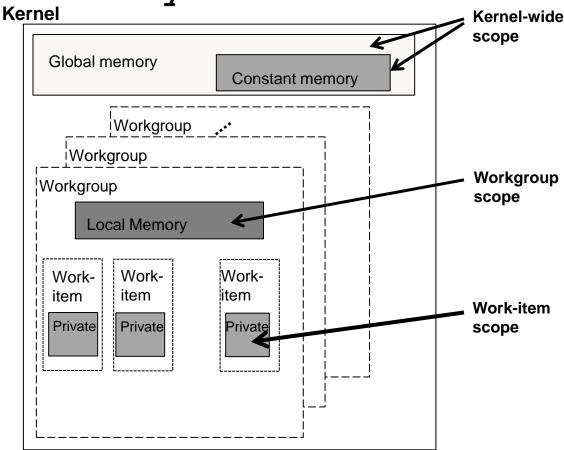

# **GPU Thread Organisation**

- Reflects the memory hierarchy of the device

- All threads from a single block are executed in the same MP

# Shared memory:

- Used for communication and synchronization of thread of the same block

- How to map neuronal processing and communications into CUDA threads?

**NVIDA : CUDA – Data Parallelism**

#### Data Parallelism

- It refers to the program property whereby many arithmetic operations can be safely performed on the data structure in a simultaneous manner.

- The concept of Data Parallelism is applied to typical matrix-matrix computation.

#### **NVIDIA GPU Computing - CUDA Kernels and Threads**

#### **NVIDIA GPU Computing - CUDA Kernels and Threads**

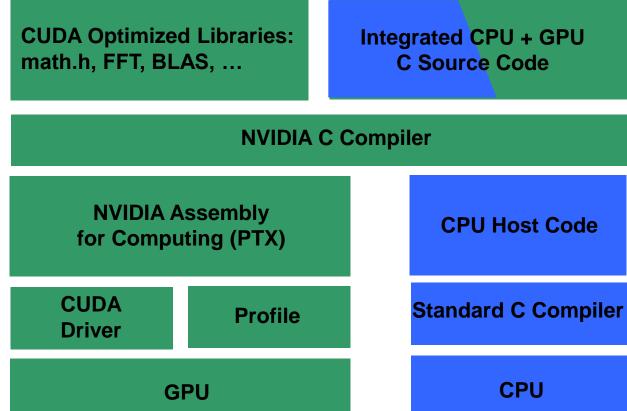

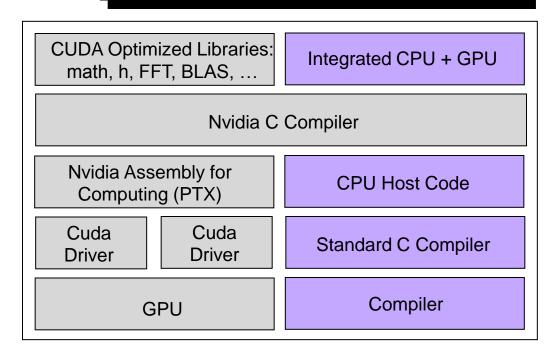

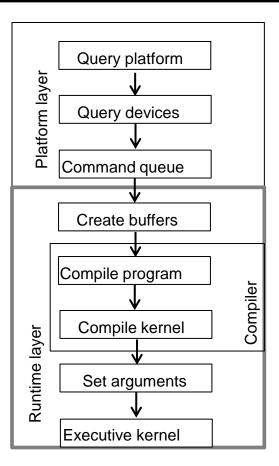

### **CUDA Software Development**

#### **CUDA Performance Advantage**

NVIDIA CUDA platform for parallel processing on Nvidia GPUs. Key elements are common C/C++ source code with different compiler forks for CPUs and GPUs; function libraries that simplify programming; and a hardware-abstraction mechanism that hides the details of the GPU architecture from programmers. Source : NVIDIA, References

#### **NVIDIA GeForce GPU**

- The future of GPUs is programmable processing

- So build the architecture around the processor

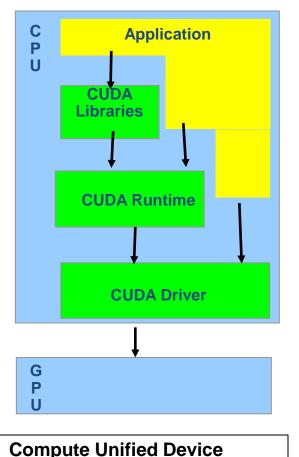

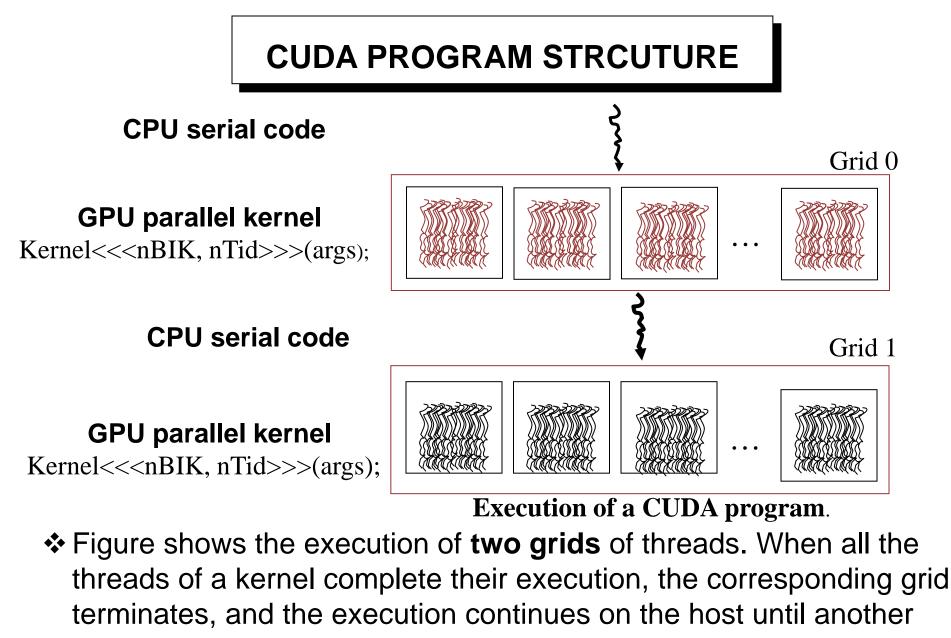

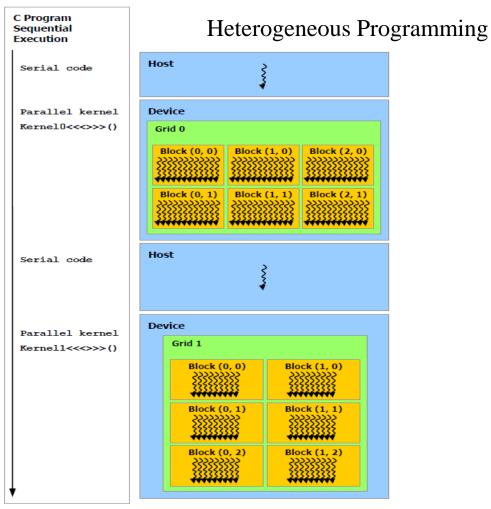

### CUDA PROGRAM STRCUTURE

- A CUDA program consists of one or more phases that are executed on either the host (CPU) or a device such as GPU.

- The phases that exhibit **little** or **no data parallelism** are implemented in the **host** code.

- The phases **rich amount of data** parallelism are implemented in the **device** code.

- A CUDA program is a unified source code encompassing both host and device code.

- The NVIDIA C Compiler (nvcc) separates the two during the compilation process. The host-code is straight ANSI C code

- The device code is written using ANSCI key-words for labeling data-parallel functions called kernels and their associated data structures. Source & Acknowledgements : NVIDIA, References

#### An approach to Writing CUDA Kernels

- Use algorithms that can expose substantial parallelism, you'll need thousands of threads...

- Identify ideal GPU memory system to use for kernel data for best performance

- Minimize host/GPU DMA transfers, use pinned memory buffers when appropriate

- Optimal kernels involve many trade-offs, easier to explore through experimentation with microbenchmarks based key components of the real science code, without the baggage

- Analyze the real-world use cases and select the kernel(s) that best match, by size, parameters, etc.

Source : NVIDIA, References

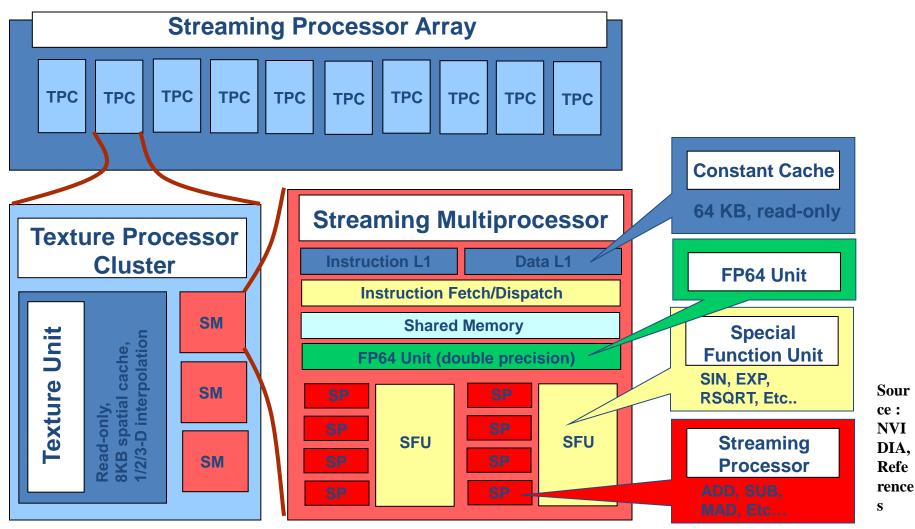

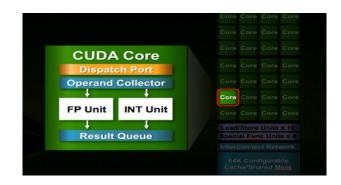

#### **Processor Terminology**

- SPA \$

- ✓ Streaming Processor Array (variable across GeForce 8-series, 8 in GeForce8800)

- ✤ TPC

- ✓ Texture Processor Cluster (2 SM + TEX)

- SM

- ✓ Streaming Multiprocessor (8 SP)

- ✓ Multi-threaded processor core

- Fundamental processing unit for CUDA thread block

- SP SP

- ✓ Streaming Processor

Source : NVIDIA, References

✓ Scalar ALU for a single CUDA thread

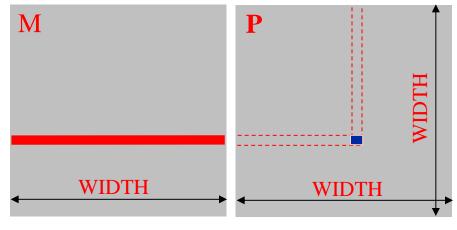

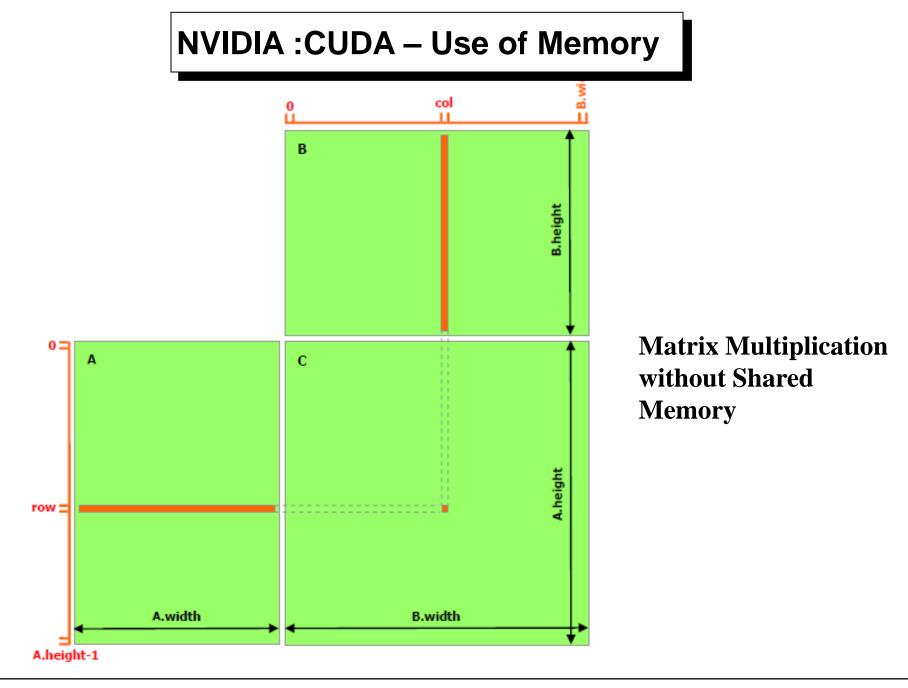

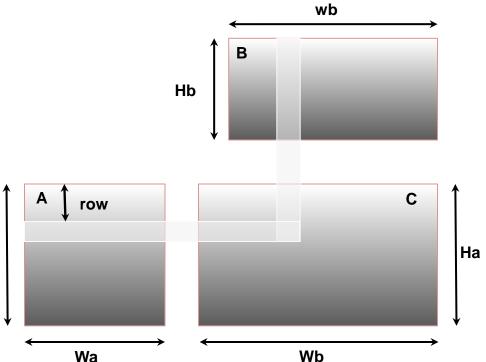

#### NVIDA :CUDA – Data Parallelism

- Data Parallelism : It refers to the program property whereby many arithmetic operations can be safely performed on the data structure in a simultaneous manner

- Example : The concept of Data Parallelism is applied to typical matrix-matrix computation.

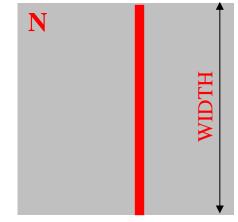

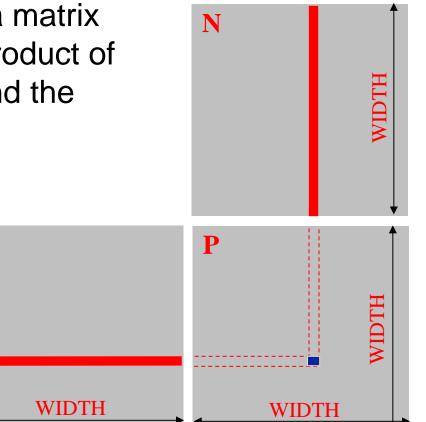

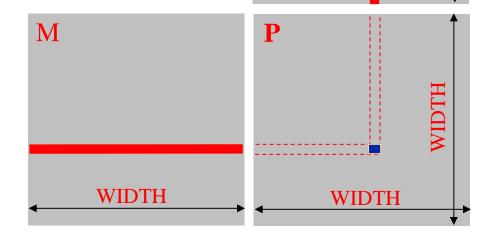

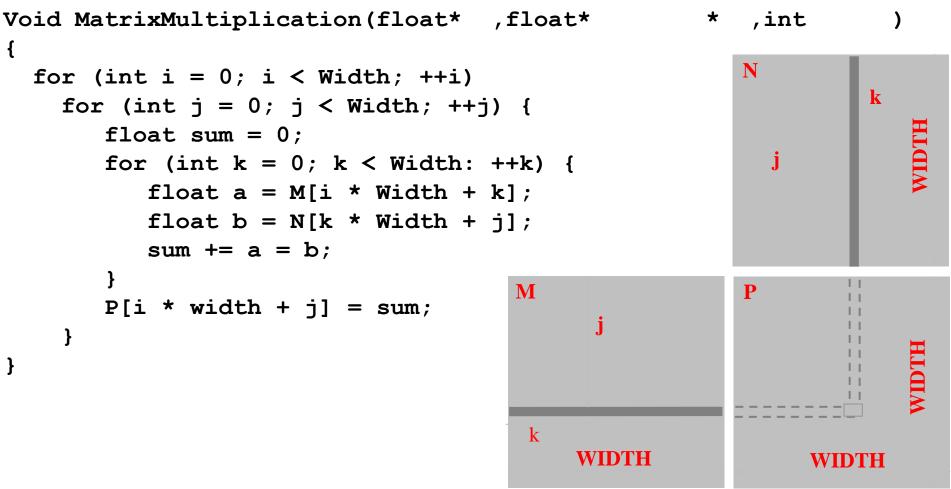

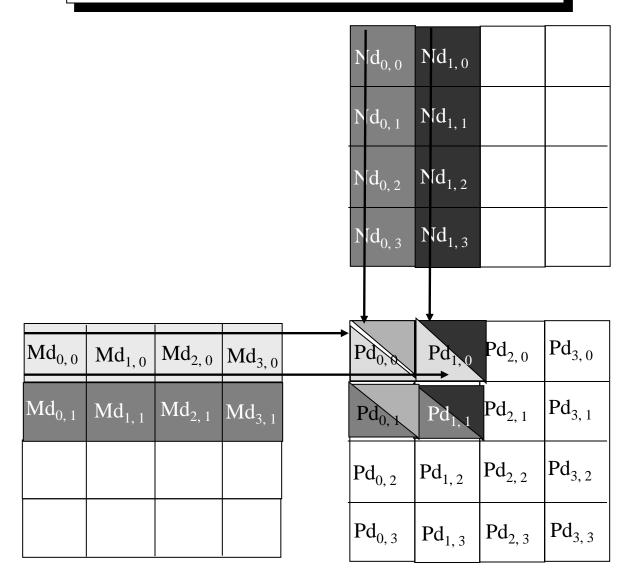

- Each element of the product matrix P is generated by performing a dot product between a row of input matrix M and a column of input matrix N as shown in figure.

Figure Data parallelism in matrix multiplication.

#### **NVIDA : CUDA – Data Parallelism**

M

- In figure, highlighted elements of a matrix

P is generated by taking the dot product of the highlighted row of matrix M and the highlighted column of matrix N

- Note : Dot product operations for computing different matrix

P elements can be simultaneously performed.

- None of these dot products will affect the results of each other.

Figure Data parallelism in matrix multiplication.

NVIDA :CUDA – Data Parallelism

- **♦** For **P** = (1000 X 1000); **M** = (1000 X 1000) & **N** = (1000 X 1000)

- The number of dot products : 1,000,000

- Each dot product involves 1000 multiply and 1000 accumulate arithmetic operations

### Note :

- Data Parallelism in real application is not as simple as matrix-matrix multiplication.

- Different forms of Data parallelism exists in several applications

N

#### Figure : Data parallelism in matrix Multiplication.

WIDTH

### CUDA PROGRAM STRCUTURE

- The device code is complied by the *nvcc* and executed on a GPU device.

- Refer CUDA Software Development Kit (SDK) are implemented in the host code.

#### \* About Kernel function :

- Generate a large number of threads to exploit parallelism

- In Matrix into Matrix Multiplication algorithm, the kernel that uses one thread to compute one element of output matrix P would generate *1,000,000 threads* when it is invoked.

### CUDA PROGRAM STRCUTURE

### Remarks :

- CUDA threads are of much lighter weight than the CPU threads

- It can be assumed that these threads take very few cycles to generate and schedule due to efficient hardware support.

- <u>Note</u> : <u>CPU</u> threads that typically require thousands of clock cycles to generate and schedule.

- When kernel function is invoked or launched, all the **threads** that are generated take advantage of **data parallelism.**

- All the threads that are generated by a kernel during an invocation are collectively called a **grid**.

kernel is invoked. Source & Acknowledgements : NVIDIA, References

#### **NVIDA : CUDA STRUCTURE**

#### **Example 1. : Matrix Multiplication**

```

int main (void) {

Step 1 : // allocate and the initialize the matrices M,N, P

// I/O read the input matrices M & N

• • • • • • • • • • • •

Step 2 : // M * N on the device

MatrixMultiplication (M,N,P, Width)

Step 3 : // I/O to write the Output matrix P

// Free matrices M,N, P

.....

return 0;

}

```

### **NVIDIA : CUDA STRUCTURE**

#### **Example : Matrix Multiplication**

Figure A simple matrix multiplication function with only host code.

## NVIDIA :CUDA STRUCTURE

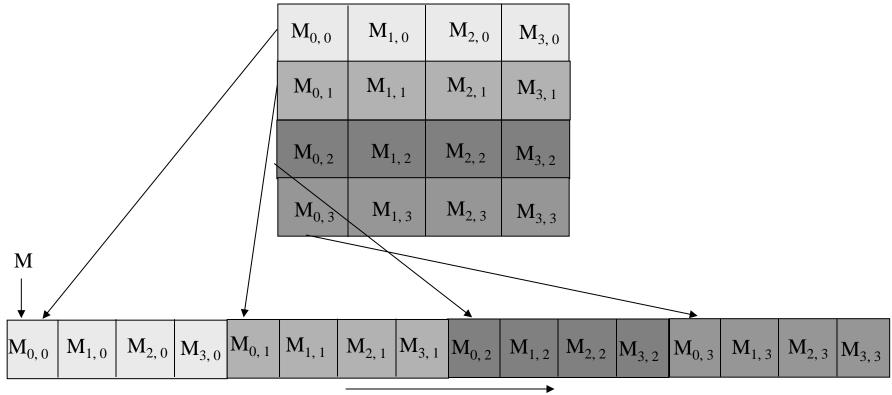

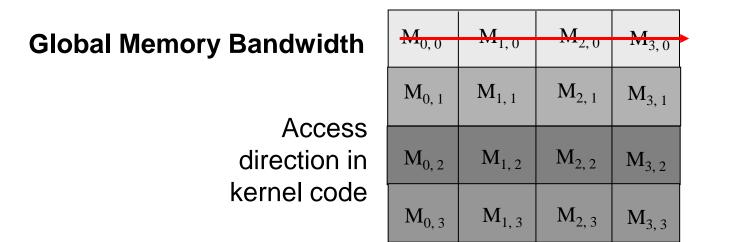

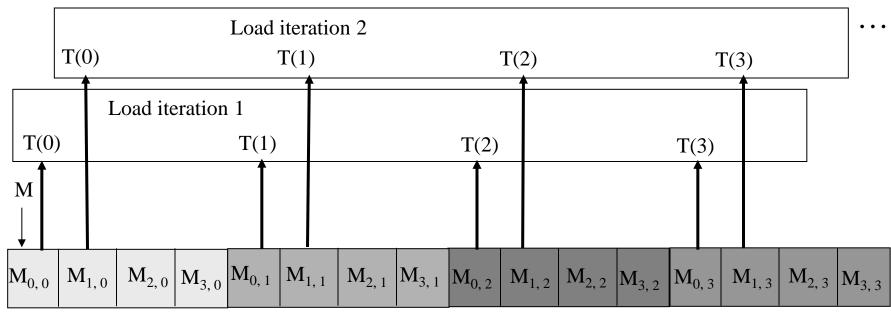

### **Example : Matrix Multiplication**

**Note :** 4 x 4 matrix is placed into 16 consecutive memory locations (Simple code can be written using Standard C language.)

| M <sub>0,0</sub>  | M <sub>1,0</sub>  | M <sub>2,0</sub>  | M <sub>3,0</sub>  |

|-------------------|-------------------|-------------------|-------------------|

| M <sub>0, 1</sub> | M <sub>1, 1</sub> | M <sub>2, 1</sub> | M <sub>3, 1</sub> |

| M <sub>0, 2</sub> | M <sub>1, 2</sub> | M <sub>2, 2</sub> | M <sub>3, 2</sub> |

| M <sub>0, 3</sub> | M <sub>1,3</sub>  | M <sub>2, 3</sub> | M <sub>3, 3</sub> |

$\mathbf{M}$

| M <sub>0,0</sub> | <b>M</b> <sub>1,0</sub> | M <sub>2,0</sub> | M <sub>3,0</sub> | M <sub>0, 1</sub> | M <sub>1, 1</sub> | M <sub>2, 1</sub> | M <sub>3, 1</sub> | M <sub>0,2</sub> | M <sub>1, 2</sub> | M <sub>2, 2</sub> | M <sub>3,2</sub> | M <sub>0,3</sub> | M <sub>1,3</sub> | M <sub>2,3</sub> | M <sub>3,3</sub> |

|------------------|-------------------------|------------------|------------------|-------------------|-------------------|-------------------|-------------------|------------------|-------------------|-------------------|------------------|------------------|------------------|------------------|------------------|

|                  |                         |                  |                  |                   |                   |                   |                   |                  |                   |                   | ,                |                  |                  |                  |                  |

Placement of two-dimensional array elements into the linear address system memory.

### **NVIDIA : CUDA STRUCTURE**

#### **Example 2: Matrix Multiplication**

Revised host code simple matrix multiplication that moves the matrix multiplication to a device

```

Void MatrixMultiplication(float* M,float* N,float* P,int Width)

{

int size = Width * Width *sizeof(float);

float* Md, Nd, Pd;

Step 1: // Allocate device memory for M, N, and P

// copy M and N to allocate device memory locations

Step 2: // Kernel invocation code - to have the device to

// perform the actual matrix multiplication

Step 3: // copy P from the device memory

// free device matrices

}

Source & Acknowledgements : NVIDIA, References

```

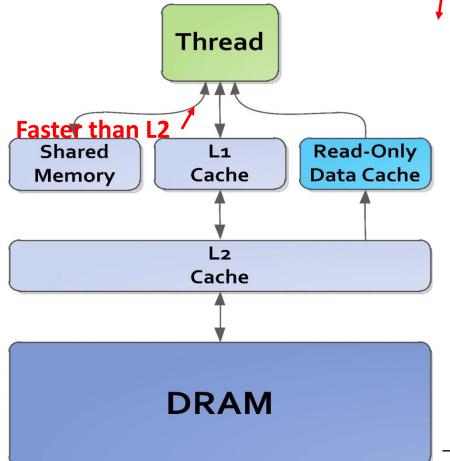

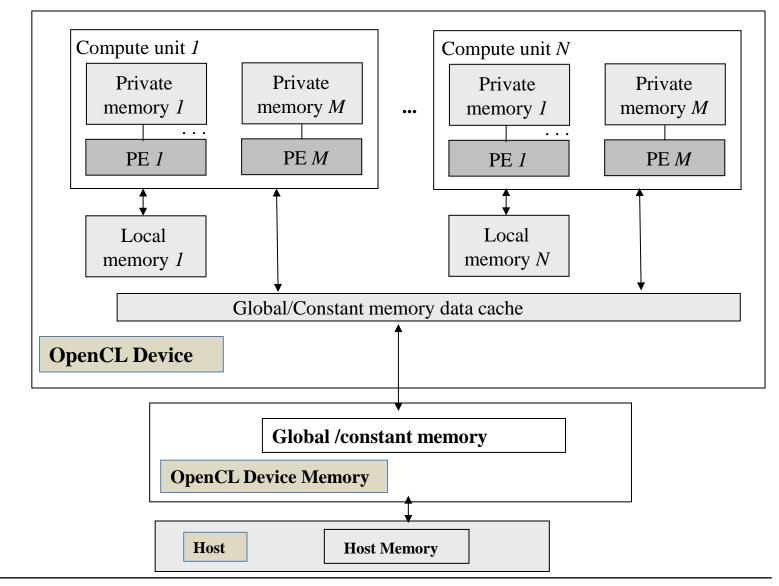

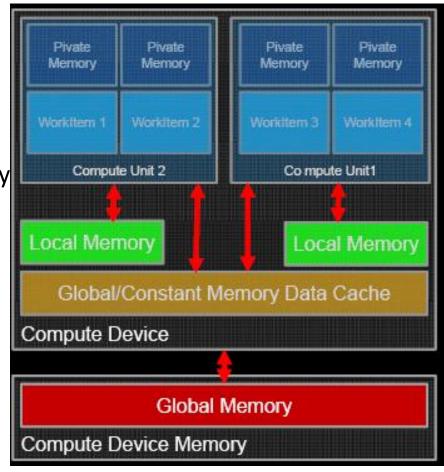

# **CUDA** Architecture

## **CUDA Device Memories and Data Transfer**

- -Processor:

- -Set of Multi-Processors (MP)

- -Set of Scalar Processor (SP)

## -Memory:

- –High b/w global memory

- -Fast shared memory (per SP)

## -Execution:

- -Kernel program on GPU

- -Threads scheduling in warps

# **Basic Implementation on GPU**

Source & Acknowledgements : NVIDIA, References

C-DAC hyPACK-2013 An Overview of CUDA enabled NVIDIA GPUs

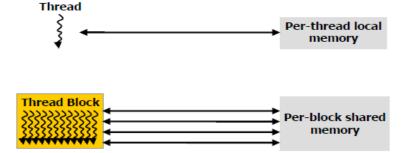

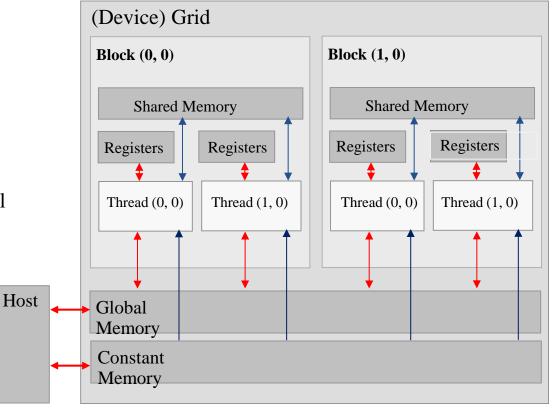

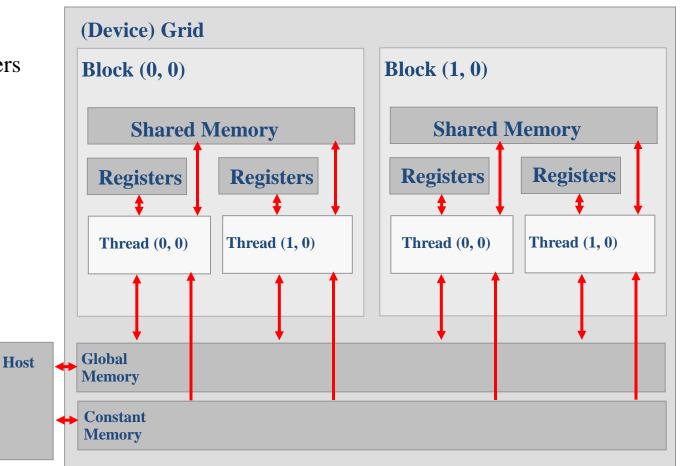

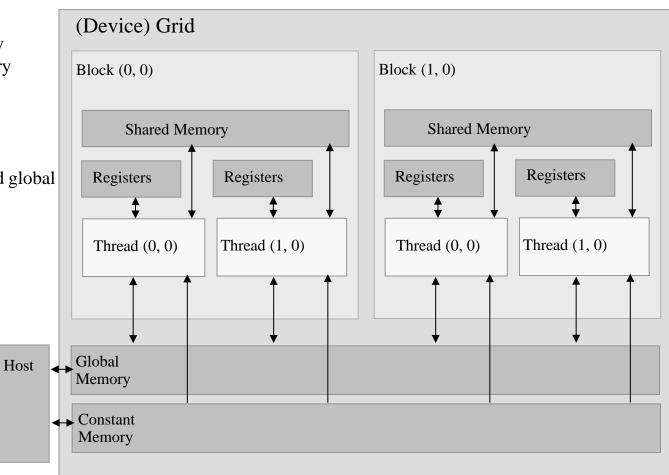

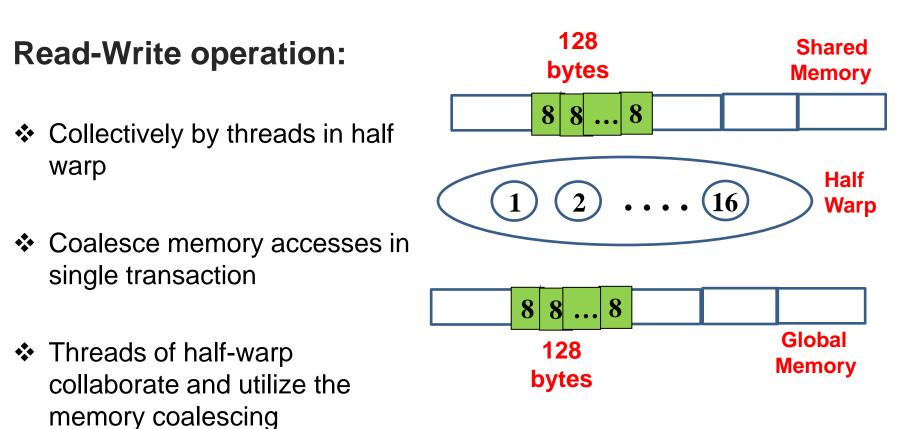

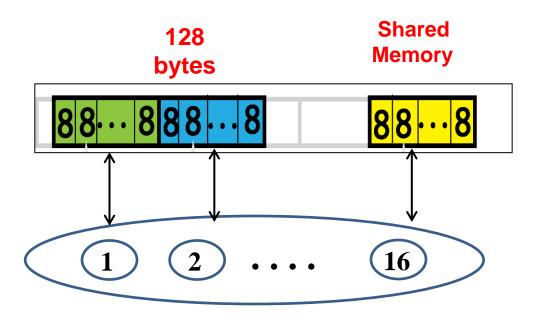

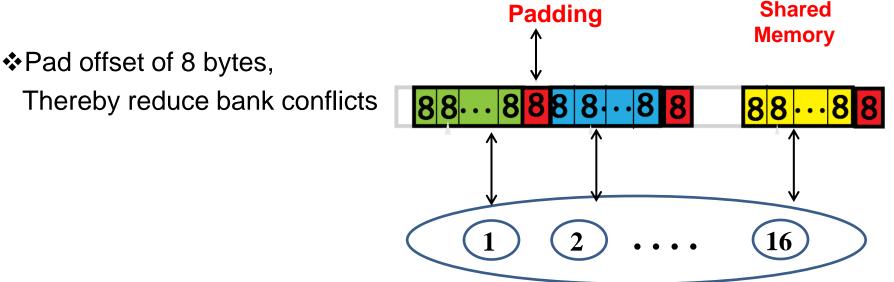

## NVIDA : CUDA DEVICE MEMORIES & DATA TRANSFER

#### CUDA device memory model & Data transfer

#### • Device code can:

- R/W per-thread registers

- R/W per-thread local memory

- R/W per-block shared memory

- R/W per-grid global memory

- Read only per-gold constant

#### - Host code can

- Transfer data to/from per-grid global and constant memories

- Isolah memory & constant memory -devices host code can transfer to and from the device, as illustrated by the bidirectional arrows between these memories and host

Host memory is not shown in the figure

## NVIDA : CUDA DEVICE MEMORIES & DATA TRANSFER

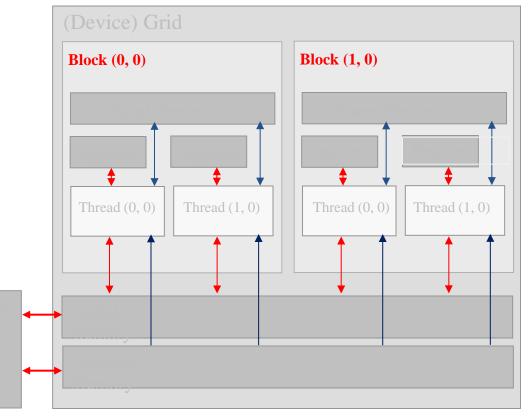

(Device) Grid

Shared Memory

Registers

Thread (1, 0)

**Block (0, 0)**

Registers

Thread (0, 0)

#### CUDA device memory model & data transfer

- cudaMalloc()

- Allocates object in the device global memory

- Two parameters

- Address of a pointer to the allocated object

- **Size of** allocated object terms of bytes

• cudaFree ()

Frees object from device global Host memory

• Pointer to freed object

CUDA API functions for device global memory management

Global

Memory

Constant Memory

Source & Acknowledgements : NVIDIA, References

**Block** (1, 0)

Registers

Thread (0, 0)

Shared Memory

Registers

Thread (1, 0)

#### **NVIDIA : CUDA STRUCTURE**

#### **Example : Matrix Multiplication**

```

Void MatrixMultiplication(float* M,float* N,float* P,int Width)

{

int size = Width * Width *sizeof(float);

float* Md, Nd, Pd;

Step 1: // Allocate device memory for M, N, and P

// copy M and N to allocate device memory locations

Step 2: // Kernel invocation code - to have the device to

// perform the actual matrix multiplication

Step 3: // copy P from the device memory

// free device matrices

}

```

## NVIDA :CUDA DEVICE MEMORIES & DATA TRANSFER

#### CUDA device memory model & data transfer

- cudaMemcpy()

- Memory data transfer

- Requires four parameters

- Pointer to destination

- Pointer to source

- Number of bytes copied

- Type of transfer

- Host to Host

- Host to Device

- Device to Host

- Device to Device

- Transfer is asynchronous

- CUDA API functions for data transfer between memories

Source & Acknowledgements : NVIDIA, References

rs ed Hock (0, 0) Fread (0, 0) Thread (1, 0) Hock (1, 0) Thread (0, 0) Thread (1, 0) Thread (0, 0) Thread (1, 0) Thread (1, 0) Thread (1, 0)

### **NVIDIA : CUDA STRUCTURE**

#### **Device Memory & Data transfer**

**cudaMalloc()** : Called from the host code to allocate a piece of global memory for an object.

```

float* Md

int size = Width * Width *sizeof(float);

cudaMalloc( (void**)&Md, size);

......

cudaFree(Md);

```

- 1. The first parameter of the cudaMalloc() function is the address of a pointer variable that must point to the allocated object after allocation

- 2. The second parameter of cudaMalloc() function gives size of the obejct to be allocated.

- 3. After the computation, cudaFree() is called with pointer Md as input to free the storage space for the Matrix from the device global memory.

### **NVIDA : CUDA STRUCTURE**

#### **Device Memory & Data transfer**

CUDA Programming Environment : Two symbolic constants cudaMemcpy(Md,M,size, cudaMemcpyHostToDevice);

cudaMemcpy(P,Pd,size, cudaMemcpyDeviceToHost);

are predefined constants of the CUDA Programming Environment.

**Note :** The **cudaMemcpy()** function takes four parameters

- 1. The first parameter is a pointer destination location for the copy operation

- 2. The second parameter points to the source data object to be copied

- 3. The third parameter specifies the number of bytes to be copied

- 4. The fourth parameter indicates the types of memory involved in the copy: from the host memory to host memory; from host memory to device memory; from device memory to host memory

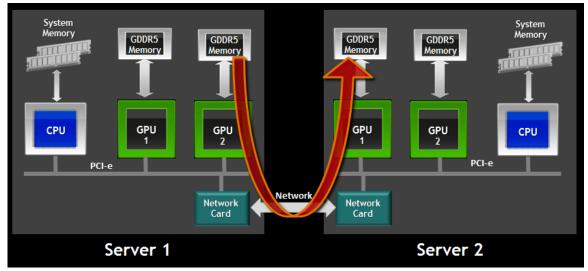

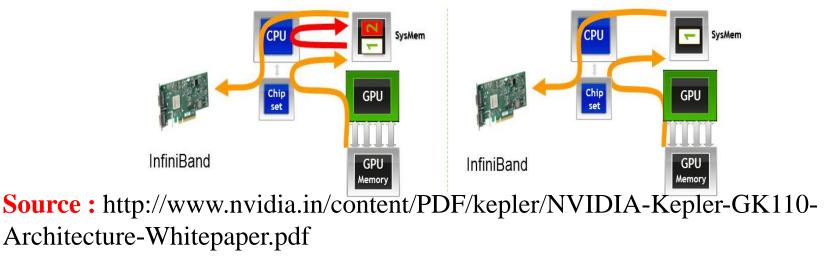

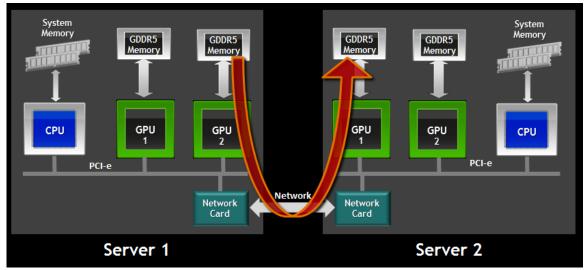

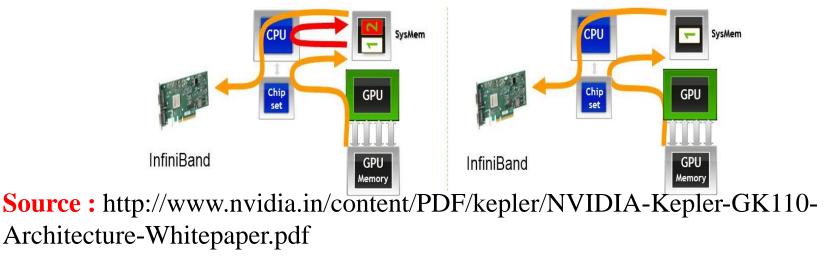

- **Note :** Please note that **cudaMemcpy() cannot** be used to copy between different GPUs to multi-GPU systems.

## NVIDIA :CUDA STRUCTURE

#### **Device Memory & Data transfer**

```

The revised MatrixMultiplication() function Code

Void MatrixMultiplication(float* M,float* N,float* P,int Width)

{

int size = Width * Width *sizeof(float);

float* Md, Nd, Pd;

Step 1. // Transfer of M and N to device memory

cudaMalloc( (void**) &Md, size);

cudaMemcpy(Md,M,size, cudaMemcpyHostToDevice);

cudaMalloc( (void**) &Nd, size);

cudaMemcpy(Md,M,size, cudaMemcpyHostToDevice);

// Allocate P on the device

cudaMalloc ( (void**) &Pd, size)

Step 2. // Kernel Invocation code

Step 3. // Transfer P from device to host

cudaMemcpy(P,Pd,size, cudaMemcpyDeviceToHost);

// free device matrices

cudaFree(Md); cudaFree(Nd); cudaFree(Pd);

}

Source & Acknowledgements : NVIDIA, References

```

### **KERNEL FUNCTIONS AND THREADING**

CUDA kernel function is declared by "\_\_\_global\_\_\_" keyword

This function will be executed on the device and can only called from the host to generate a **grid of threads** on a device.

Besides "\_\_global\_\_", there are two other keywords tha can be used in front of a function declaration.

\_\_device\_\_ float DeviceFun( )

\_\_global\_\_ void KernelFun()

\_host\_\_ float HostFunc( )

**NVIDIA : CUDA STRUCTURE**

#### **KERNEL FUNCTIONS AND THREADING**

CUDA extensions to C function declaration

\_\_device\_\_ float DeviceFun(): Declared as a CUDA device function)

\_\_host\_\_ float HostFunc() :Declared as a CUDA host function)

|                                   | Executed on the : | Only calling from the : |

|-----------------------------------|-------------------|-------------------------|

| device float DeviceFun( )         | device            | device                  |

| global void KernelFun( )          | device            | host                    |

| <pre>host float HostFunc( )</pre> | host              | host                    |

### **KERNEL FUNCTIONS AND THREADING**

The MatrixMultiplication() Kernel function

\_\_global\_\_\_ void MatrixMulKernel(float\* Md, float\* Nd, float\* Pd, int Width)

```

{

// 2D Thread ID

Int tx = threadId.x;

Int ty = threadId.y;

// P value stores the Pd element that is computed by the

// thread

float Pvalue = 0;

for (int k = 0; k < width; ++k) {

float Mdelement = Md[ty * width + k];

float Ndelement = Nd[k * width + tx];

Pvalue += Mdelement * Ndelement;

}

// Write the matrix to device memory each thread writes one

// element

Pd[ty*Width + tx ] = Pvalue;

} // Limitation : Can handle only matrices of 16 elements in

each dimension

```

### **KERNEL FUNCTIONS AND THREADING**

The MatrixMultiplication() Kernel function \_\_global\_\_\_void MatrixMulKernel(float\* Md, float\* Nd, float\* Pd, int Width)

Dot product loop uses threadIdx.x and threadIdx.y to identify the row of Md and column of Nd to work on

### Limitations

- Can handle only matrices of 16 elements in each dimension (Due to fact that the kernel function does not use blockIdx)

- Limited to using only one block of threads

- It is assumed that each block can have upto 512 threads, we can limit to 16 X 16 because 32 X 32 requires more than 512 threads per block.

- Question: How to accommodate larger matrices ? (Hint: Use multiple thread blocks)

### **KERNEL FUNCTIONS AND THREADING**

#### threadIdx.x & threadIdx.y

- Refer to the thread indices of a thread (Different threads will see different values in their threadIdx.x and threadIdx.y variables)

- Refer thread as **Thread***threadIdx.x, threadIdx,y* Coordinates reflect a multi-dimensional organization for the threads.

- CUDA threading hardware generates all of the threadIdx.x and threadIdx.y variables for each thread.

- These work on particular part of data structure of the designed code and with these thread indices allow a thread to access the hardware registers at runtime that provides the identifying coordinates to the thread.

## **KERNEL FUNCTIONS AND THREADING**

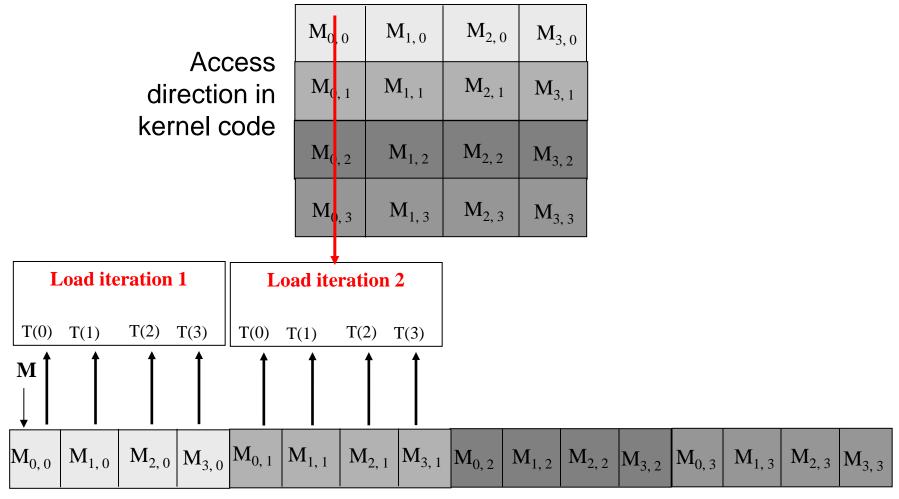

threadIdx.x; threadIdx.y in CUDA matrix multiplication

- Each thread uses its threadIdx.x and threadIdx.y to identify the row of Md and the column of Nd to perform the dot product operation.

- Each thread also uses its *threadIdx.x* and *threadIdx.y* values to select the Pd element that it is responsible for; for example *threadId<sub>2,2</sub>* will perform a dot product between column 2 of Nd and row 3 of Md and write the result into element (2,3) of Pd. This way, the threads collectively generate all the elements of the Pd matrix.

- When a kernel is invoked or launched, it is executed as *grid* of parallel threads & each CUDA thread grid typically is comprised of thousands to millions of lightweight GPU threads per kernel invocation.

Source & Acknowledgements : NVIDIA, References

# **NVIDIA : KERNEL FUNCTIONS AND THREADING**

#### \*A Thread block

- A thread block is a batch of threads that can co-operate with other by

- Synchronizing their execution

- ➢ For hazard-free shared memory accesses

- Efficiently sharing data through a low-latency shared memory

- \* Cop-operation thread blocks

- Two threads from two different blocks can not cooperate

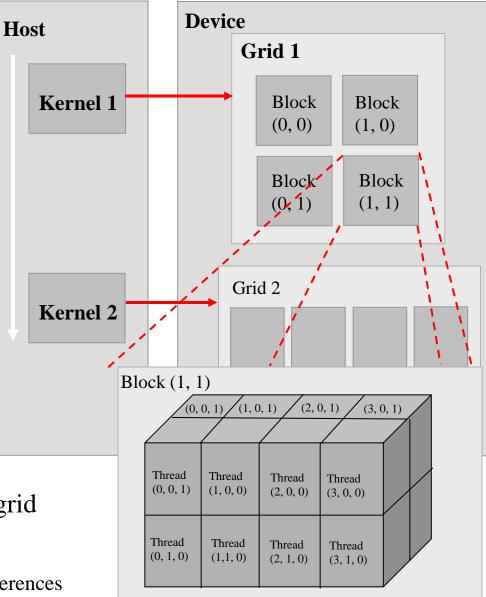

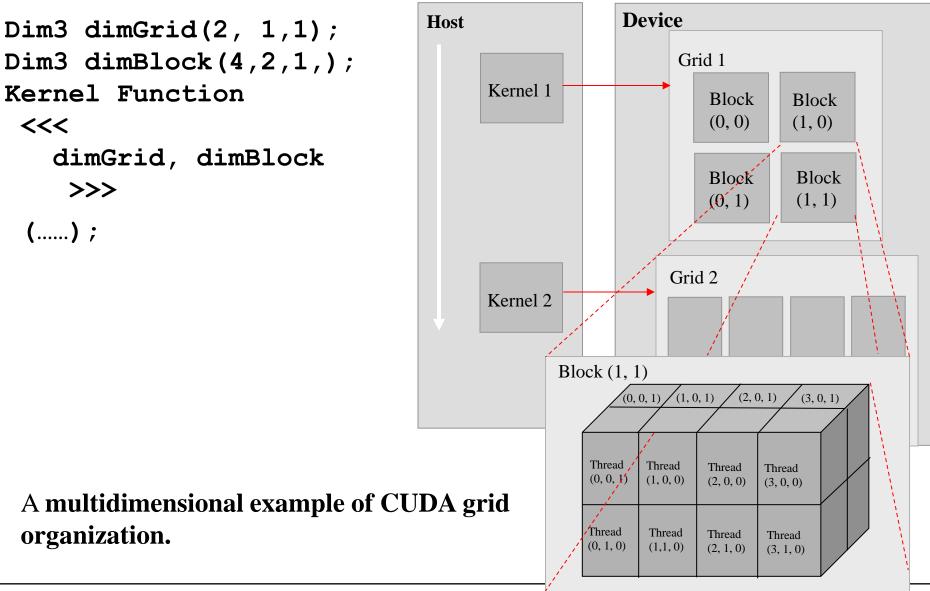

- A multidimensional example of CUDA grid organization.

#### **NVIDIA : CUDA Thread Organisation**

#### **Ex : Vector Vector Addition**

```

// Kernel definition

global void VecAdd(float* A, float* B, float* C)

int i = threadIdx.x;

c(i) = A[i] + B[i];

}

int main ()

// Kernel invocation with N Threads

VecAdd<<<1, N>>>(A, B, C);

}

```

#### Kernel

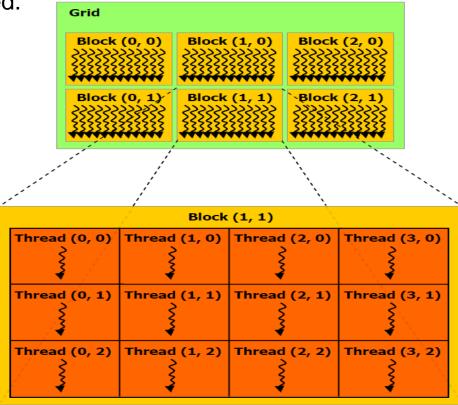

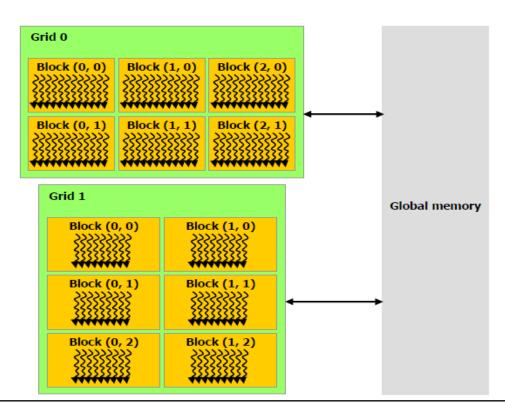

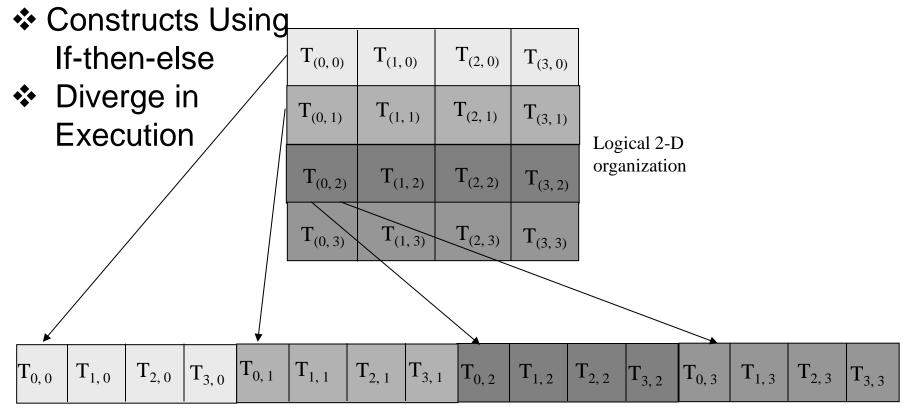

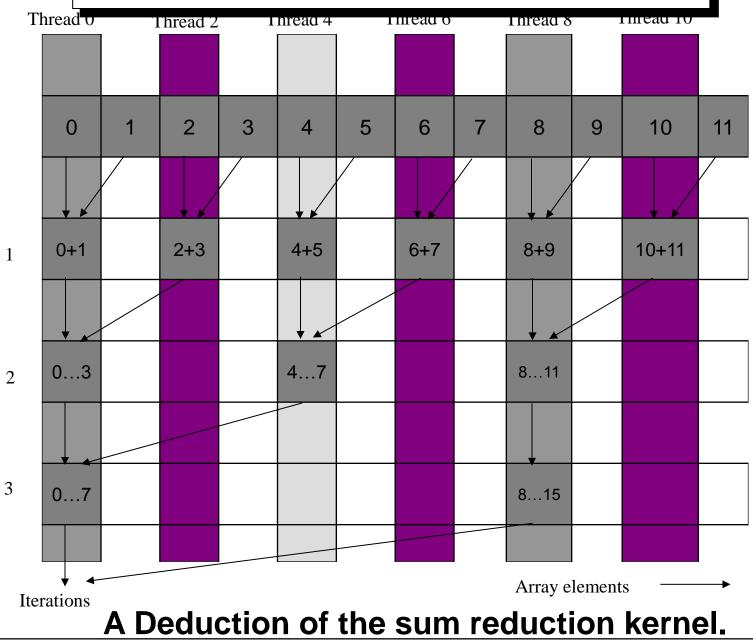

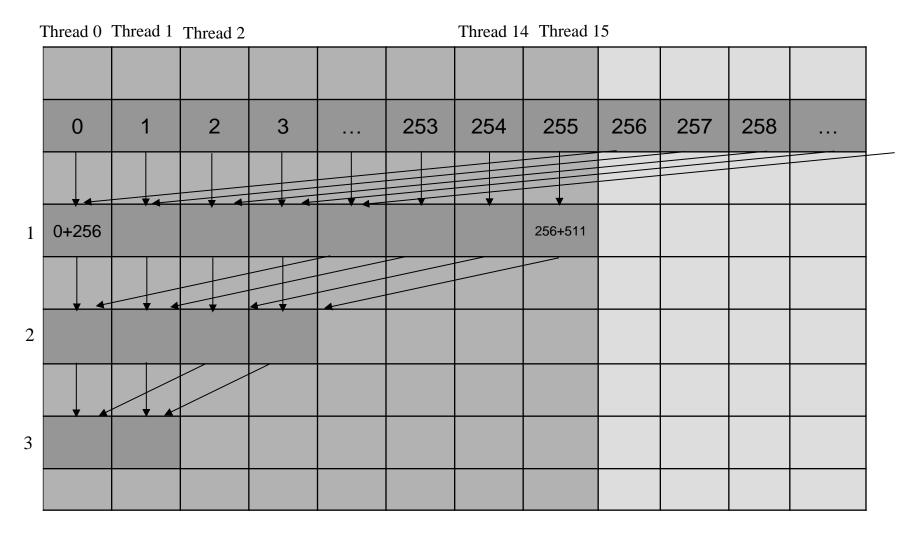

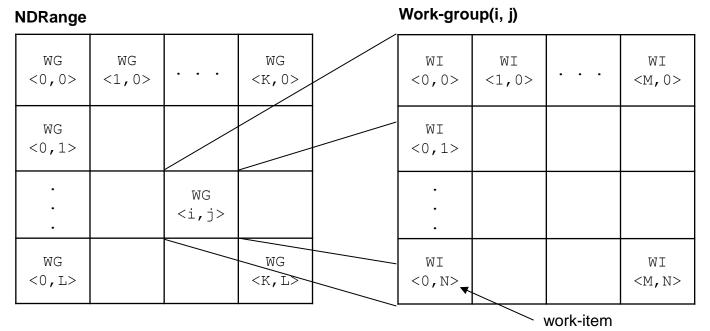

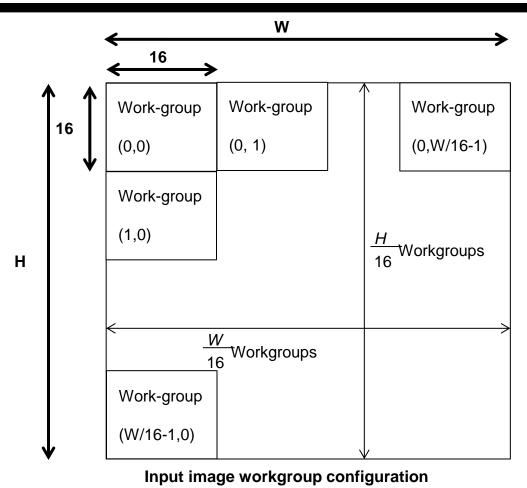

#### KERNEL FUNCTIONS AND THREADING Organization of Threads in a grid - CUDA

- Threads in a grid are organized into a two-level hierarchy, as illustrated in figure (Refer earlier slide)

- At the top level, each grid consists of one or more thread blocks. All blocks in a grid have the same number of threads

- Example : In figure (Refer earlier slide), **Grid 1** is organized as a 2 X 2 array of 4 blocks.

- Each block has a unique two-dimensional co-ordinate given by the CUDA specific keywords blockIdx.x and blockId.y

- All thread blocks must have the **same** number of threads organized in the same manner Source : NVIDIA

KERNEL FUNCTIONS AND THREADING Organization of Each Thread block in a grid

- Each thread block is, in turn, organized as a three dimensional array of threads with a total size up to 512 threads

- The coordinates of threads in a block are uniquely defined three thread indices : threadIdx.x, threadIdx.y and threadIdx.z

- Note : Not all applications will use all three (3) dimensions of a thread block

- **\*Example :** (Refer earlier slide)

- Each thread block is organized into a 4 x 2 x 2 threedimensional array of threads

- This gives a Grid one (1) a total of 4 x 16 = 64 threads

KERNEL FUNCTIONS AND THREADING Organization of Each Thread block in a grid

Example of host code that launches a kernel

//Setup the execution configuration

dim3 dimBlock(Width, Width);

dim3 dimGrid(1,1);

// Launch the device computation threads !

MatixmultKernel<<< dimGrid, dimBlock>>> (Md, Nd, Pd, Width);

#### **KERNEL FUNCTIONS AND THREADING**

**Observations - Example 4:** (Refer earlier slide 40)

- Code does not use any block index in accessing input and output data.

- Threads with the same threadIdx values from different blocks would end-up accessing the same input and output data elements.

- ✤ As a result, the kernel can use only one thread block.

- The theadIdx.x and threadIdx.y values are used to organize the block into a row-dimensional array of threads.

#### **KERNEL FUNCTIONS AND THREADING Observations - Example 4:** (Refer earlier slide 40)

Because a thread block can have only up to 512 threads, each thread calculates one element of the product matrix in Example 4, the code can only calculate a product matrix upto 512 elements.

#### Conclusions :

- The solution is not scalable & not acceptable due to choice of one thread block

- 2. To have a sufficient amount of data parallelism to benefit from execution on a device use of multiple blocks is required.

#### Question to be addressed

How to set the grid and thread block dimensions?

Source : NVIDIA

How to specify execution configuration parameters ?

# KERNEL FUNCTIONS AND THREADING Organization of Each Thread block in a grid //Setup the execution configuration dim3 dimBlock(Width, Width); dim3 dimGrid(1,1); // Launch the device computation threads ! MatixmultKernel<<< dimGrid, dimBlock>>> (Md, Nd, Pd, Width);

• Two struct variable of type dim3 are declared

- The **first** is for describing the configuration of blocks, which are defined as 16 x 16 groups of threads.

- The second variable, dimGrid, describes the configuration of the grid.

In this example, we have only (1 X 1) block in each grid.

# Part-II(B)

# An Overview of CUDA enabled NVIDIA GPUs: CUDA Threads

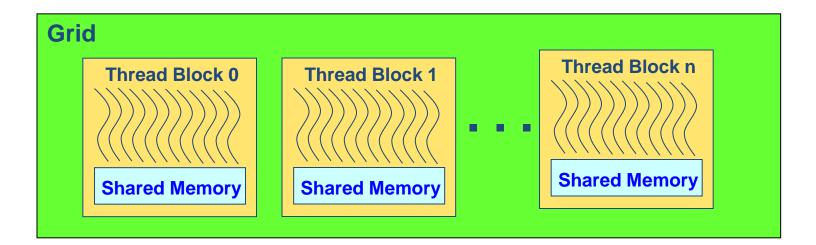

#### **CUDA Thread Organization**

- ✤ All threads in a grid execute the same kernel

- Rely on unique coordinates to distinguish themselves from each other and to identity the appropriate portion of the data to process.

- The threads are organized into a two-level hierarchy using unique coordinates

- >blockIdx (for block index) and

- threadIdx (for thread index)

(Assigned to them by the CUDA runtime system)

The gridDim and blockDim are additional built-in, pre-initialized variables that can be accessed within kernel functions

### **CUDA Thread Organization**

- ✤ All threads in a grid execute the same kernel

- Rely on unique coordinates to distinguish themselves from each other and to identity the appropriate portion of the data to process.

- Size /Dimension of Grid or Block

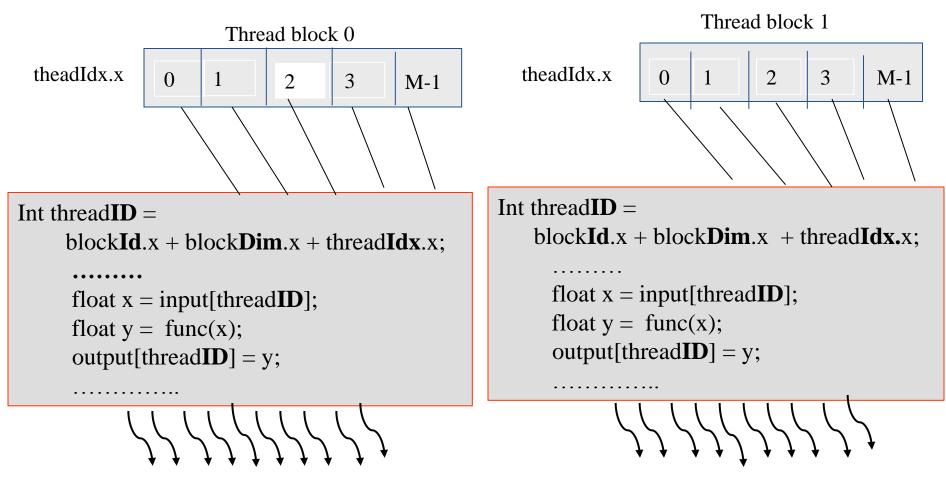

- The blockIdx and threadIdx appear as built-in, preinitialized variables that can be accessed within kernel functions

#### **CUDA Thread Organization**

- The yellow color box of each threads block in Figure shows a fragment of the kernel code

- > Part of the input data is **read** and

- > Part of the output data is write

#### **CUDA Thread Organization**

- The example figure consists of N thread blocks, each with a blockIdx.x value ranges from 0 to N-1

- Each block in-turn consists of M threads, each with a threadIDx.x value ranges from 0 to M-1.

- All blocks at each grid level are organized as a one-dimensional (1D) array

- All threads within each block level are organized as a 1D array and each grid has a total of N\*M threads

- **Example :** The black box of each thread block in figure 6 shows a fragment of the kernel code.

- The code fragment uses the

```

Int threadI = blockId.x + blockDim.x + threadIdx.x;

```

to identify the part of (a) input data to read from and (b) the part of the (b) output data structure to write to.

Dim3 dimGrid(128, 1,1);

Dim3 dimBlock(32,1,1,);

Kernel Function <<< dimGrid, dimBlock >>> (...);

You can also use

Kernel Function << 128, 32 >>> (...);

- The values of gridDim.x and gridDim.y can range from 1 to 65535

- The values of gridDim.x and gridDim.y can be calculated based on other variables at kernel launch time.

#### **NVIDIA GPU Computing - CUDA Kernels and Threads**

# **Thread Batching**

Kernel launches a grid of thread blocks

- Threads within a block cooperate via shared memory

- Threads within a block can synchronize

- Threads in different blocks cannot cooperate

Allows programs to transparently scale to different GPUs

#### **CUDA Thread Organization**

The example figure consists of N thread blocks, each with a blockIdx.x value ranges from 0 to N-1

Each block in-turn consists of M threads, each with a

threadIDx.x value ranges from 0 to M-1.

**Example :** The code fragment uses the

```

Int threadI = blockId.x + blockDim.x + threadIdx.x;

```

to identify the part of (a) input data to read from and (b) the part of the (b) output data structure to write to.

| Thread 3        | of Block | <b>0</b> has a | threadId | value | of | 0*M | + | 3 |

|-----------------|----------|----------------|----------|-------|----|-----|---|---|

| Thread 3        | of Block | <b>1</b> has a | threadId | value | of | 1*M | + | 3 |

| Thread <b>3</b> | of Block | <b>2</b> has a | threadId | value | of | 2*M | + | 3 |

| Thread <b>3</b> | of Block | <b>3</b> has a | threadId | value | of | 3*M | + | 3 |

| Thread <b>3</b> | of Block | <b>4</b> has a | threadId | value | of | 4*M | + | 3 |

| Thread 3        | of Block | <b>5</b> has a | threadId | value | of | 5*M | + | 3 |

#### **CUDA Thread Organization**

- The example figure consists of N thread blocks, each with a blockIdx.x value ranges from 0 to N-1

- Each block in-turn consists of M threads, each with a threadIDx.x value ranges from 0 to M-1.

- Each grid has a total of N\*M threads

- **Example :** Assume a each grid **128** blocks (N = 128) and each block has 32 (M=32) threads and a total of 128\*32 = 4096 threads in the grid.

- Access to **blockDim** in the kernel function returns 32

Thread 3 of Block 0 has a threadId value of 0\*32 + 3 = 3Thread 3 of Block 4 has a threadId value of 4\*32 + 3 = 131Thread 3 of Block 20 has a threadId value of 20\*32 + 3 = 643Thread 3 of Block 40 has a threadId value of 40\*32 + 3 = 1283Thread 10 of Block 80 has a threadId value of 80\*32+10 = 2570Thread 3 of Block 100 has a threadId value of 100\*32+3 = 3203Thread 15 of Block 102 has a threadId value of 102\*32+15 = 3279Thread 16 of Block 120 has a threadId value of 120\*32+16 = 3856

#### **CUDA Thread Management – An Overview**

**CUDA Thread Management – An Overview**

- Each thread of the 4096 threads has its own unique threaded value

- Kernel code uses threadID variable to index into the input[] array and output[] arrays.

- If we assume that both arrays are declared with 4096 elements, then each thread may take one of the input[] of elements and produce one of the output[] elements

- Performance depends upon input[] array and output[] arrays

## CUDA – Grid ; Host Code to launch the kernel

Dim3 dimGrid(128, 1,1); Dim3 dimBlock(32,1,1,); Kernel Function <<< dimGrid, dimBlock >>> (...);

The execution configuration parameters are between <<< and >>>

The Scalar values can also be used for the execution configuration parameters if a gird or a block has only one dimension. For example

Kernel Function << 128, 32 >>> (...);

## CUDA – Grid

- In CUDA, a grid is organized as a 2D array or blocks.

- Grid Organization is determined by the execution of configuration provided at kernel launch )

dim3 dimGrid(128, 1,1);

- The **first** parameter specifies the dimensions of each block in terms of number of blocks

- The second parameter specifies the dimensions of each block in terms of number of threads

- Each such parameter is a dim3 type, which is essentially a

C struct with three unsigned integer filed : x, y, and z.

- The third parameter –grid dimension parameter is set to 1 for clarity. (Because of grids are 2D array of blocks dimensions)

- The exact organization of a grid is determined by the execution configuration provided at kernel launch.

- CUDA Grid ; Host Code to launch the kernel

Dim3 dimGrid(128, 1,1);

Dim3 dimBlock(32,1,1,);

Kernel Function <<< dimGrid, dimBlock >>> (...);

- The values of gridDim.x and gridDim.y can range from 1 to 65535

- The values of gridDim.x and gridDim.y can be calculated based on other variables at kernel launch time.

- All threads in a block share the same blockIdx value.

- blockIdx.x value ranges between 0 and gridDim.x-1

- blockIdx.y value ranges between 0 and gridDim.y-1

- Remark : Once a kernel is launched, its dimensions can not change.

**CUDA - Grid- thread blocks**

- In CUDA, a each thread block is organized into a 3D array of threads

- ✤ All blocks in a grid have the same dimensions.

- Each threadIdx consists of three components : the x-coordinate threadIdx.x, y-coordinate threadIdx.y, and z-coordinate threadIdx.z

- The exact organization of a thread block is determined by the execution configuration provided at kernel launch.

#### CUDA - Grid- thread blocks dim3 dimBlock(32, 1, 1);

- The first parameter specifies the total terms of number of blocks

- The second and third parameter specifies the number of threads in each dimension

- The configuration parameter can be accessed as a predefined C struct variable, blockDim

- Remark : The total size of a block is limited to 512 threads, with flexibility in distribution these elements into the three dimensions as long as the total number of threads does not exceed 512.

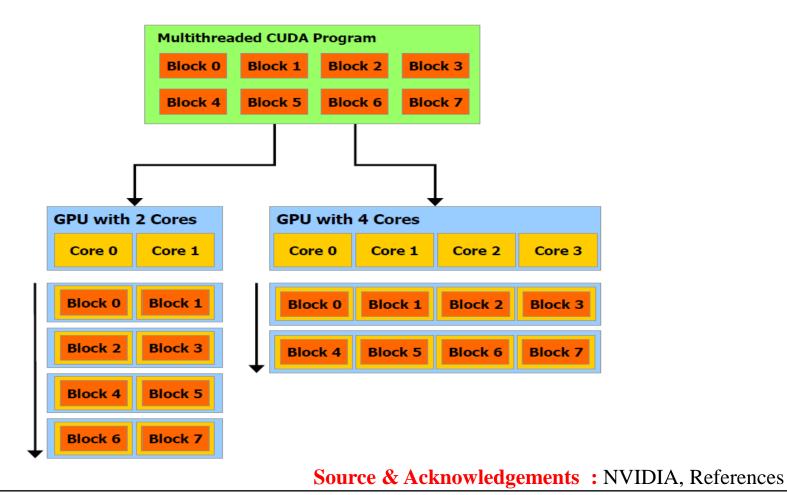

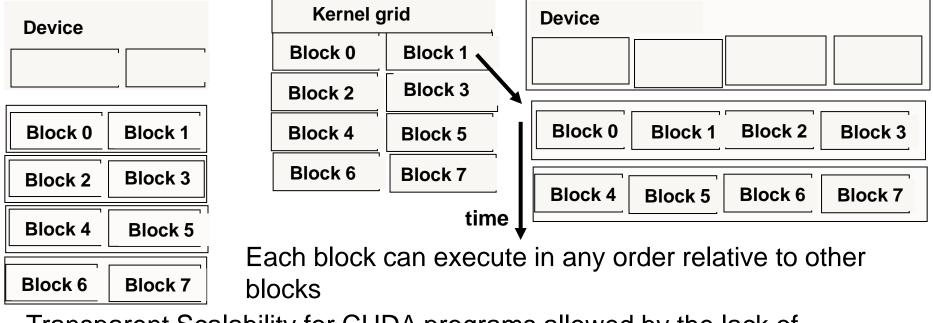

**Automatic Scalability** : A multi-threaded program is partitioned into blocks of threads that execute independently from each other, so that a GPU with more cores will automatically execute the program in less time than a GPU with fewer cores.

C-DAC hyPACK-2013 An Overview of CUDA enabled NVIDIA GPUs

**Grid of Thread Blocks :** Blocks are organized into a one-dimensional, twodimensional, or three-dimensional grid of thread blocks as illustrated by Figure. The number of thread blocks in a grid is usually dictated by the size of the data being processed or the number of processors in the system, which it can greatly exceed.

#### **NVIDIA : CUDA – Structure**

Serial code executes on the host while parallel code executes on the device.

# Part-II(C)

# An Overview of CUDA enabled NVIDIA GPUs: CUDA Synchronization

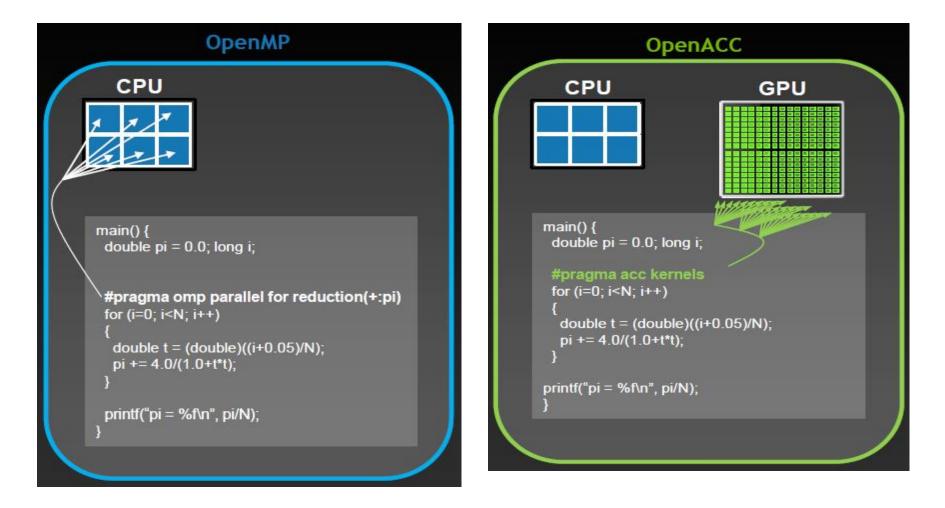

#### Synchronization and transparent scalability

- CUDA allows threads in the same block to coordinate their activities using barrier synchronization function \_\_\_\_\_syncthreads().

- Call to \_synchtreads(), ensures that all threads in a block have completed a phase of their execution of the kernel before any moves on to the next phase.

Transparent Scalability for CUDA programs allowed by the lack of synchronization constraints between locks

#### Synchronization and transparent scalability

- In CUDA a \_\_\_\_\_syncthreads() statement must be executed by all threads in a block.

- Call to \_\_syncthreads(), ensures that all threads in a block have completed a phase of their execution of the kernel before any moves on to the next phase.

Issues in CUDA Barrier Synchronization

\$ Use of \_\_synthread() statement in "if" statement

\$ Use of \_\_synthread() statement in "if-then-else" statement

- thread may perform execution of "then" path OR "if" path OR "else" path, and this leads to waiting of threads at barrier synchronization points. This results waiting for each other thread.

- The ability to synchronize also imposes execution constraints on threads within a block.

#### Synchronization and transparent scalability

Issues in CUDA Barrier Synchronization : *How to avoid excessive long waiting time ?*

- The threads in a each block should execute close time proximity with each other.

- CUDA runtime systems satisfy this constraint by assigning execution resources to all threads in a block as a unit, that is when a thread o a block is assigned to an execution resources.

- This ensures the time proximity of all threads in a block an prevents excessive waiting time during synchronization

#### Synchronization and transparent scalability

Issues in CUDA Barrier Synchronization : *How to avoid excessive long waiting time ?*

- CUDA runtime can execute blocks in any order relative to each other because none of them must wait for each other.

- Remark : The ability to execute the same application ode at a wide range of speeds allows the production of a wide range of implementation according to the cost, power, and performance requirements of particular market segment.

- In <u>CUDA</u> one can execute large number of blocks at the same time, subject to more resources exist for typical high-end implementation

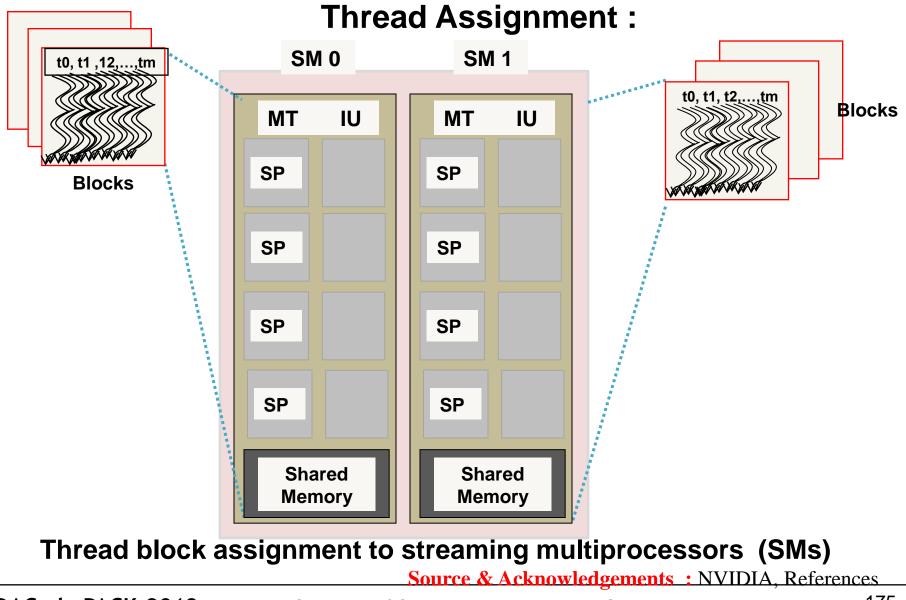

#### **Thread Assignment :**

Once the kernel is launched, CUDA runtime system generates the corresponding grid of threads.

- These threads are assigned to execution resources on a block-by-block basis.

- Thread block assignment to streaming multiprocessors (SMs)

C-DAC hyPACK-2013 An Overview of CUDA enabled NVIDIA GPUs

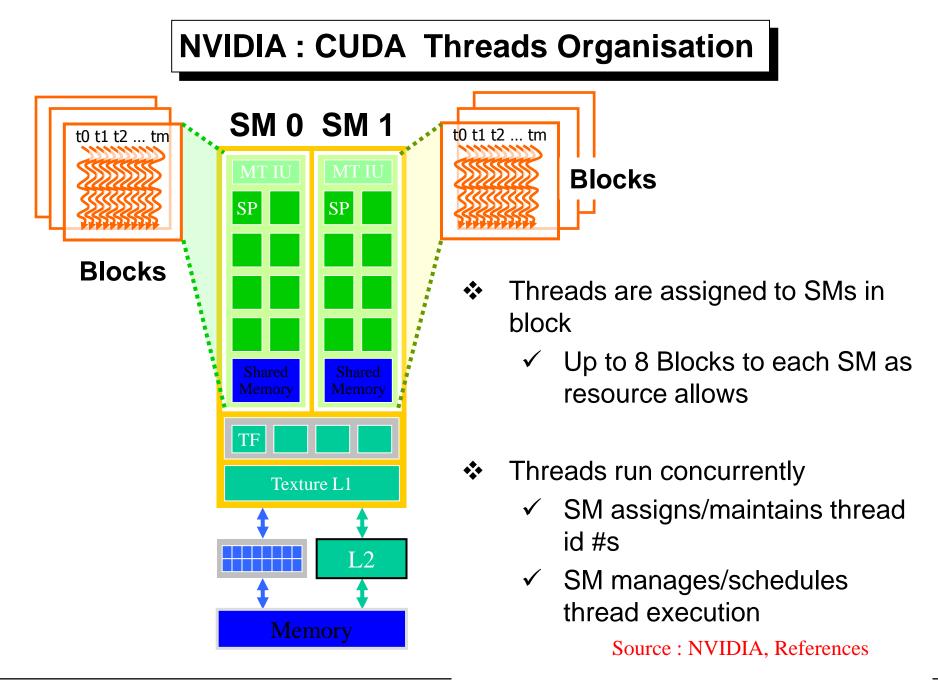

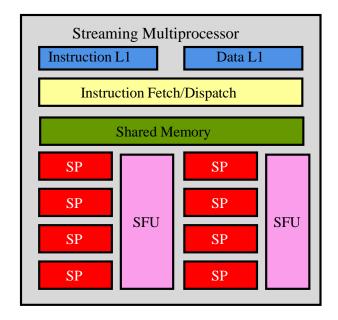

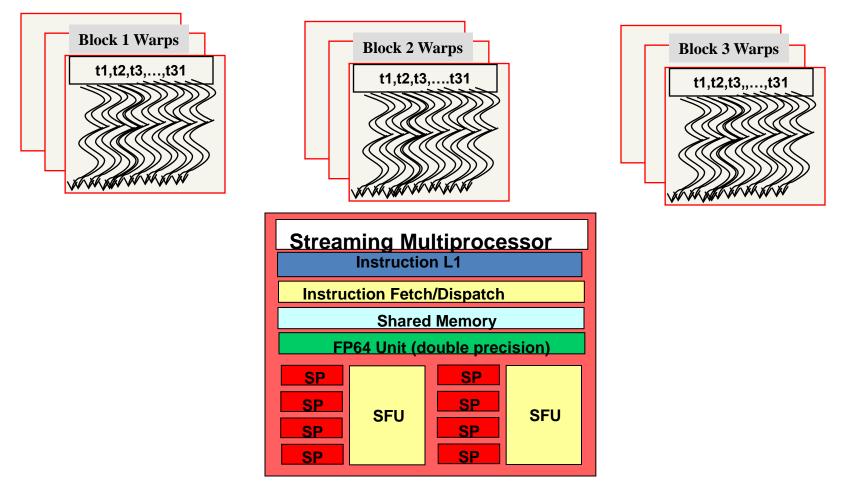

#### Streaming Multiprocessor (SM)

- Streaming Multiprocessor (SM)

- ✓ 8 Streaming Processors (SP)

- ✤ 2 Super Function Units (SFU)

- Multi-threaded instruction dispatch

- ✓ 1 to 512 threads active

- ✓ Shared instruction fetch per 32 threads

- ✓ Cover latency of texture/memory loads

- ✤ 20+ GFLOPS (24 GFLOPS in G92)

- ✤ 16 KB shared memory

- DRAM texture and memory access

#### Source : NVIDIA, References

#### **NVIDIA : CUDA Thread Scheduling & Latency Tolerance**

NVIDIA GT200 GPU Block Diagram GT200 : Tesla C1060/ S1070 Blocks partitioned into *warp* for thread scheduling

#### **Thread Assignment**

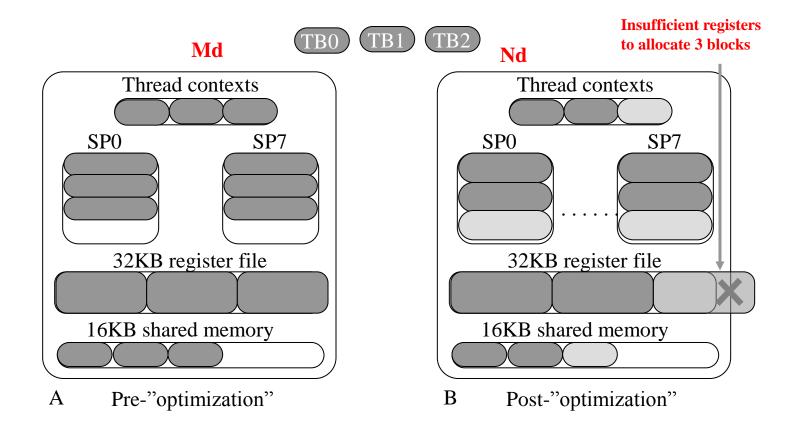

- Execution resources are organized into streaming multiprocessors

NVIDIA GT200 implementation features

- **30** Streaming Multi-Processors (**SMs**)

- 8 Threading blocks can be assigned to each SM as long as there are enough execution resources to satisfy the needs of all the blocks.

- Each threading block can have atmost **512** threads

- 240 thread blocks can be simultaneously assigned to SMs

- Upto 1024 threads can be assigned to each SM

- Maximum of **30720** threads can be simultaneously residing in the **SM**

- ✤ Most grids contain many more than 240 blocks.

- The runtime system maintains a list of blocks that need to execute and assign new blocks to SMs as they complete execution of blocks previously assigned to them.

- Note : In situations with an insufficient amount if any one or more types of resources needed for the simultaneous execution of 8 blocks , the CUDA runtime automatically reduces the number of blocks assigned to each SM until the resource usage is under the limit.

### **Thread Assignment**

- Three thread blocks assigned to each SM.

- One of the SM resource limitations is the number of threads that can be simultaneously tracked and scheduled.

- Hardware resources are required for SMs to maintain the thread, block IDs, and track their execution status.

- **Upto 1024** threads can be assigned to each SM.

- 4 blocks of 256 threads each, 8 blocks of 128 threads each ... (16 blocks of 64 threads each is not possible.)

- Execution resources are organized into streaming multiprocessors

NVIDIA GT80 implementation features

- **16** Streaming Multi-Processors (**SMs**)

- 8 Threading blocks can be assigned to each SM as long as there are enough execution resources to satisfy the needs of all the blocks.

- Each threading block can have atmost **256** threads

- Upto 768 threads can be assigned to each SM (3 blocks of 256 each; 6 blocks of 128 threads each)

- Maximum of **12288** threads can be simultaneously residing in the **SM**

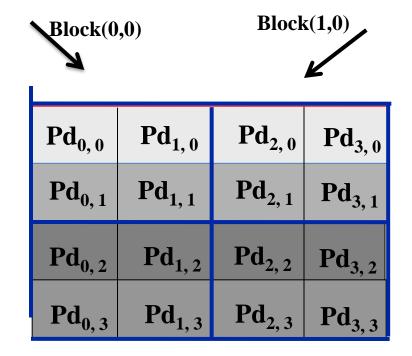

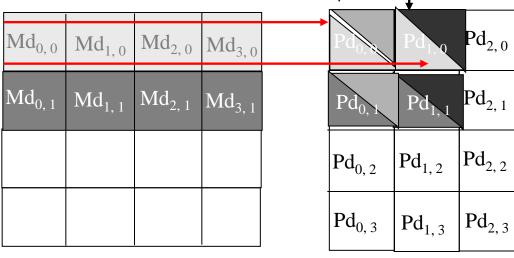

## CUDA - Grid- thread blocks

**Ex:** A multi-dimensional example of CUDA grid organization

- The grid consists of four blocks organized into a 2 X 2 array

- Each block is in figure is labeled with (blockIdx.x, blockIdx.y)

- Ex: Block (1,0) has blockIdx.x = 1, and blockIdx.y = 0

- In CUDA, total size of block is limited to 512 threads, with flexibility in distributing these elements into the three dimensions as long as the total number of threads does not exceed 512 threads. (\*\*\*\*)

- Ex: (512,1,1,), (8,16,2) and (16,16,2) are allowable blockDim values, but (32,32,1) is not allowable because the total number of threads would be 1024.

## CUDA - Grid- thread blocks

- Ex: A multi-dimensional example of CUDA grid organization

- Grid consists of 4 blocks of 16 threads each, with a grand total of 64 threads in the grid.

- Each thread block is organized into 4 X 2 X 2 arrays of threads (16 threads). (Only one block is shown because of all thread blocks in the grid have same dimension.)

- ✤ block (1,10) to show its 16 threads;

> thread (2,1,0) has

blockIdx.x = 2, blockIdx.y = 1, blockIdx.z = 0

- CUDA grid contain thousands to million of threads

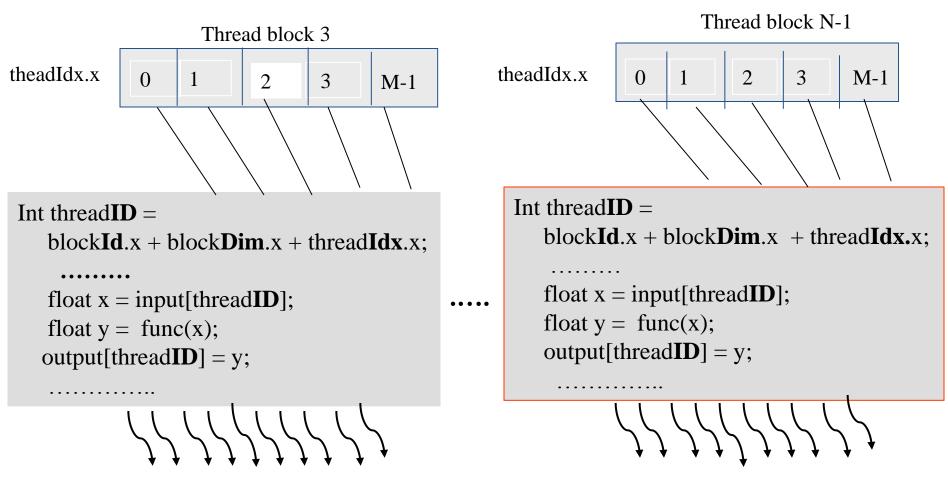

# KERNEL FUNCTIONS AND THREADING

#### threadIdx.x & threadIdx.y

- Refer to the thread indices of a thread (Different threads will see different values in their threadIdx.x and threadIdx.y variables)

- Refer thread as **Thread***threadIdx.x, threadIdx,y* Coordinates reflect a multi-dimensional organization for the threads.

- CUDA threading hardware generates all of the threadIdx.x and threadIdx.y variables for each thread.

- These work on particular part of data structure of the designed code and with these thread indices allow a thread to access the hardware registers at runtime that provides the identifying coordinates to the thread.

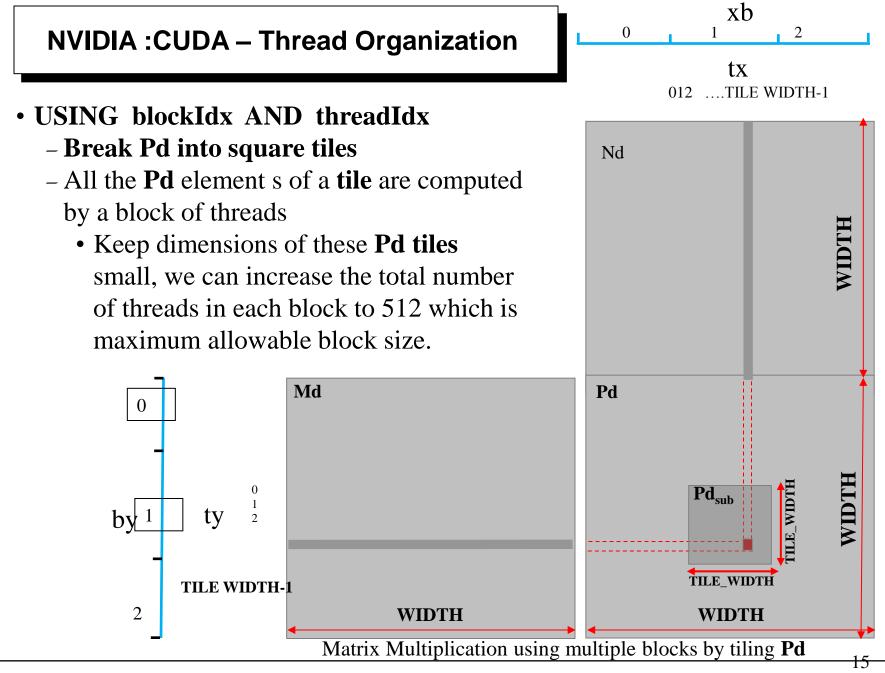

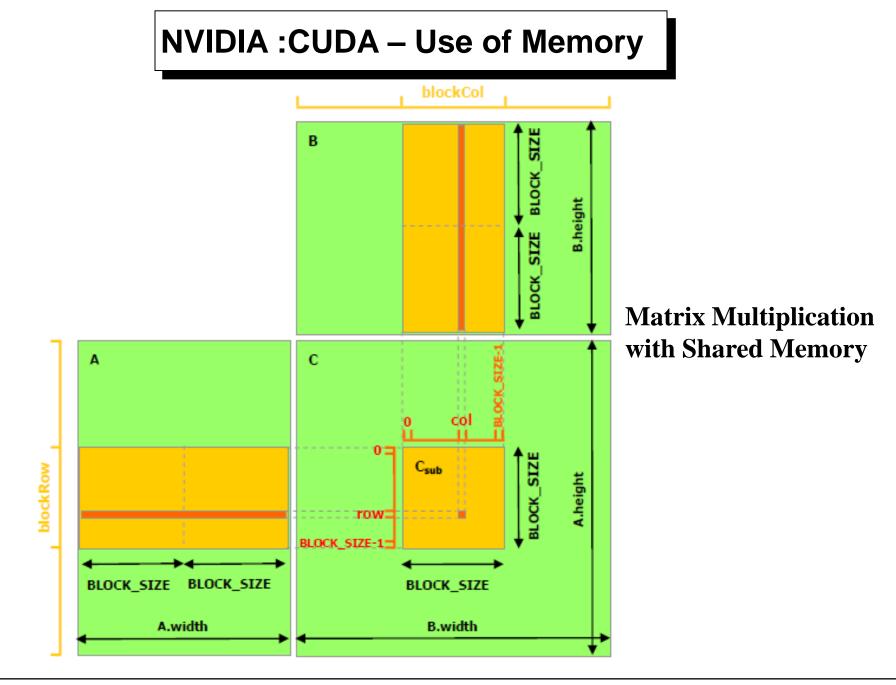

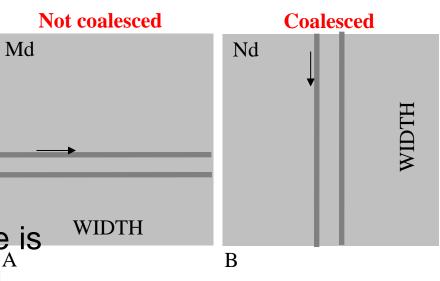

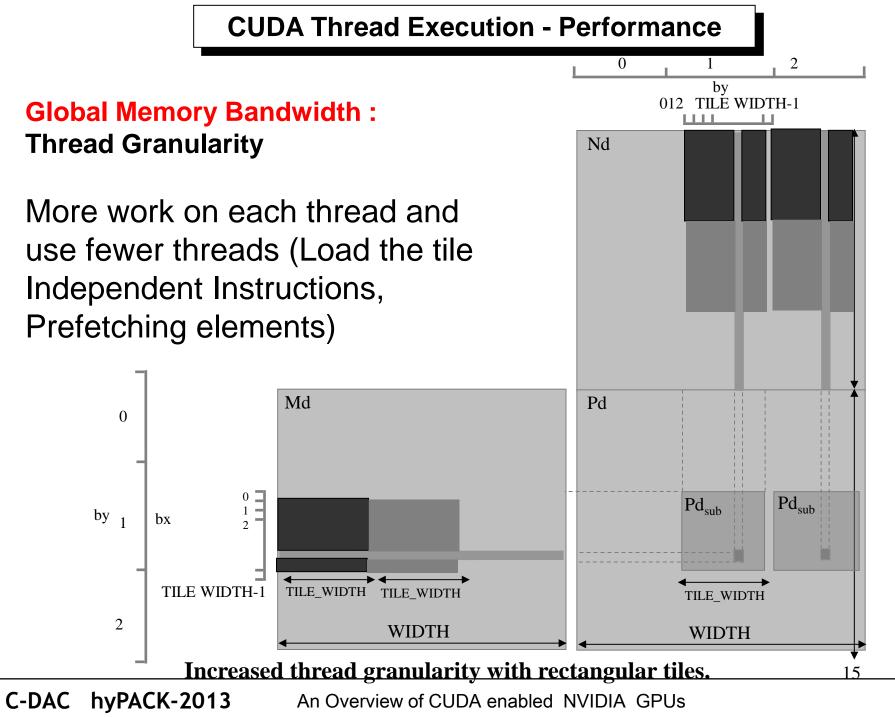

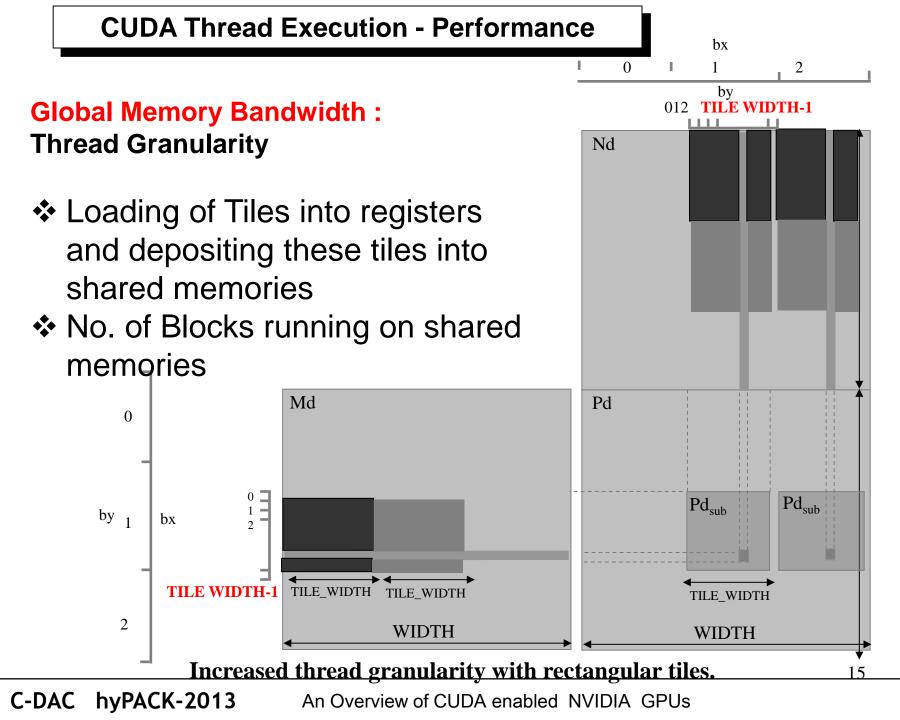

## **USING blockldx AND threadldx**

✤ For convenience sake ,

threadIdx.x and threadIdx.y as tx and ty; and blockIdx.x and blockIdx.y as bx and by.

- Each thread calculates one Pd element. The difference is that it must uses its blockIdx.x values to identify its element inside the tile.

- Each thread uses both threadIdx and blockIdx to identify the Pd element to work on.

- All threads calculating the Pd elements within a tile have the same blockIdx values

Source : NVIDIA

#### **USING blockldx AND threadldx**

- Assume that the dimensions of a block are square and are specified by the variable TILE\_WIDTH

- Each dimensions of Pd is now divided into section s of TILE\_WIDTH elements each and each block handles such a section.

- Thread can find x index and y index of Pd element i.e.

x = bx + TILE\_WIDTH + tx

$y = by + TILE_WIDTH + ty$

Pd element at respective column & row can be computed.

Source : NVIDIA