## **C-DAC Four Days Technology Workshop**

ON

## Hybrid Computing – Coprocessors/Accelerators Power-Aware Computing – Performance of Application Kernels

## hyPACK-2013

Mode 3 : Intel Xeon Phi Coprocessors

## **Lecture Notes :**

# Intel Xeon Phi Coprocessor - An Overview

Venue : CMSD, UoHYD ; Date : October 15-18, 2013

C-DAC hyPACK-2013

## An Overview of Prog. Env on Intel Xeon-Phi

### Lecture Outline

Following topics will be discussed

- Understanding of Intel Xeon-Phi Coprocessor Architecture

- Programming on Intel Xeon-Phi Coprocessor

- Performance Issues on Intel Xeon-Phi Coprocessor

## Intel Xeon Host : An Overview of Xeon - Multi-Core and Systems with Devices

# **Part-I** Background : Xeon Host - Multi-Core & Devices

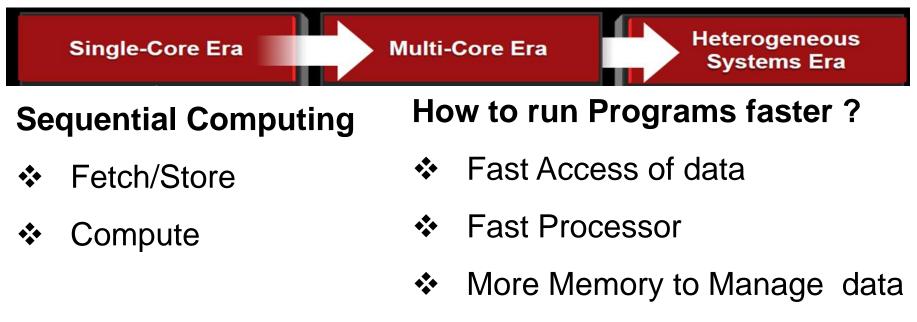

## Programming paradigms-Challenges Large scale data Computing – Current trends

# How to run Programs faster ?

# You require Super Computer

Era of Single - Multi-*to*-Many Core - Heterogeneous Computing

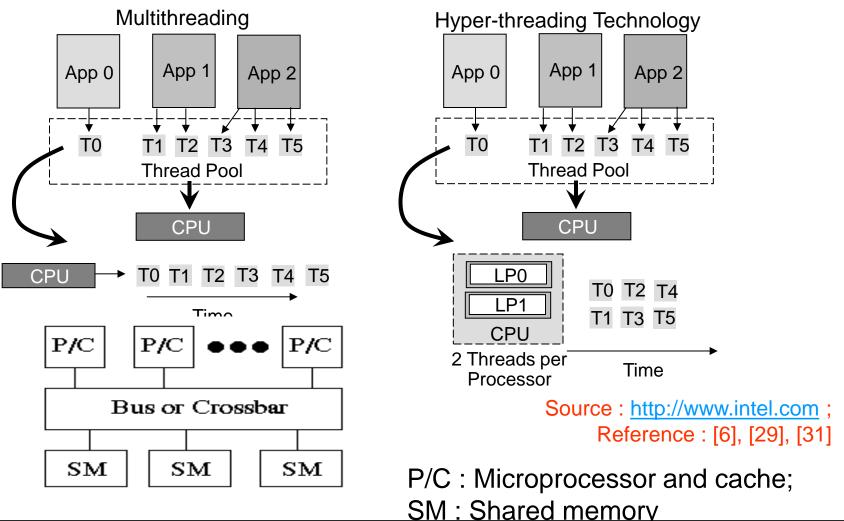

### Multi-threaded Processing using Hyper-Threading Technology

Time taken to process *n* threads on a single processor is significantly more than a single processor system with HT technology enabled.

C-DAC hyPACK-2013

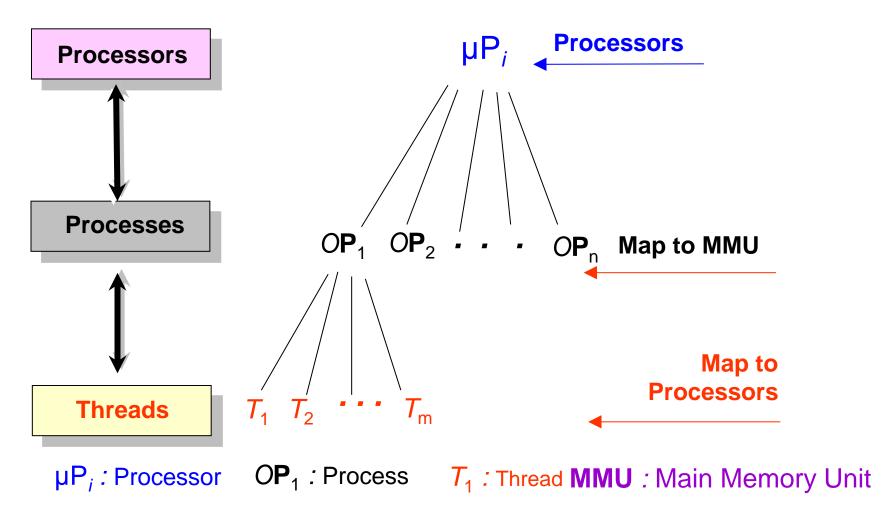

### **Relationship among Processors, Processes, & Threads**

Source : Reference [4],[6], [7]

**System View of Threads**

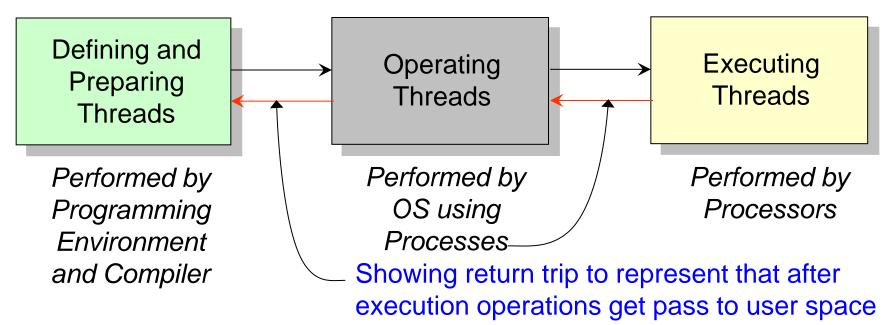

## **Threads Above the Operating System**

Understand the problems - Face using the threads – Runtime Environment

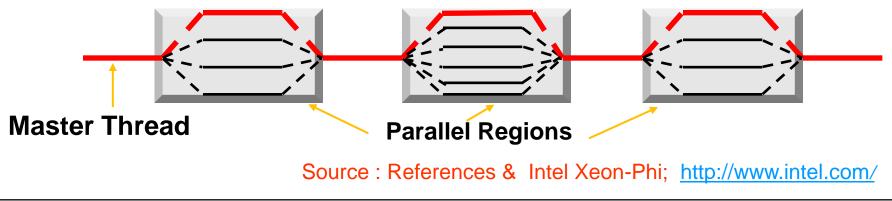

## Flow of Threads in an Execution Environment

Source : Reference [4],[6], [7]

## Architecture-Algorithm Co-Design

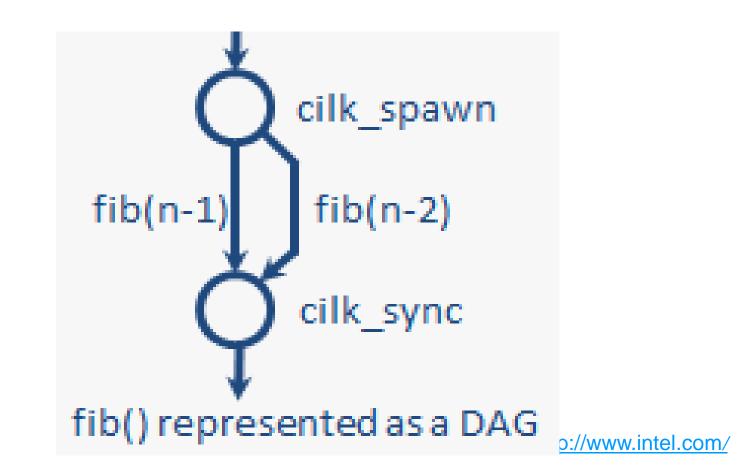

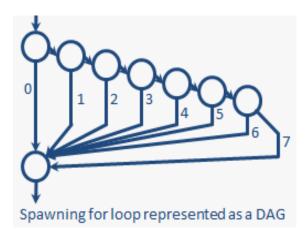

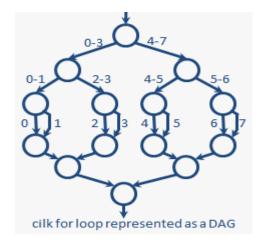

Source : <u>http://www.intel.com</u>

### System 1 : Intel Sandy Bridge Server

- ✤ Intel Software Development Platform (Intel SDP) MAK F1 Family.

- Platform : Intel (r) Many Integrated Core Architecture

- Platform Code Name : Knights Ferry

- CPU Chipset Codename : Westmere EP/ Tylersburg UP

- Board Codename : Sandy Core.

- CPU : Intel Xeon X5680 Westmere 3.33GHz 12MB L3 Cache LGA 1366 130W Six-Core Server Processor BX80614X5680

Source : <u>www.cdac.in/</u> Intel

### Intel Xeon-Host : system configuration

## System 2 : Super Micro SYS-7047GR-TPRF Server

- Chipset : Intel C602 Chipset,

- Mother board : Super X9DRG-QF,

- CPU : Intel Xeon processor E5-2643 ( quad core ) (up to 150W TDP), Support for Xeon Phi - 5110P.

- Memory : 32 GB DDR3 ECC Registered memory(1600 MHz ECC supported DDR3 SDRAM 72-bit, 240-pin gold-plated DIMMs),

- ✤ Expansion slot : with 4x PCI-E 3.0 x16 (double-width), 2x PCI-E x8),

- IPMI : Support for IPMI (Support for Intelligent Platform Management Interface v.2.0, IPMI 2.0 with virtual media over LAN and KVM-over-LAN support),

- Power : 1620W high-efficiency redundant power supply w/PMBus.

- Storage : SATA 3.0 6Gbps with RAID 0,1 support ,1 TB SATA Hard Disk,

- Network : Intel i350 Dual Port Gigabit Ethernet withsupport of Supports 10BASE-T, 100BASE-TX, and1000BASE-T, RJ45 output and 1x Realtek RTL8201N\PHY (dedicated IPMI port)

## **Intel Xeon-Host : Benchmarks Performance**

**Systems 3 : Host :** Xeon (Memory Bandwidth (BW) - Xeon: 8 bytes/channel \* 4 channels \* 2 sockets \* 1.6 GHz = 102.4 GB/s)

### **PARAM YUVA-II Intel Xeon- Node**

- Node : Intel-R2208GZ; Intel Xeon E52670;

- Core Frequency : 2.6GHz;

- Cores per Node : 16 ;

- Peak Performance /Node : 2.35 TF;

- Memory : 64 GB;

Source : <u>www.cdac.in/</u> Intel

## PARAM YUVA-II Intel Xeon- Node Benchmarks(\*)

#### Xeon Node Memory Bandwidth :

8 bytes/channel \* 4 channels \* 2 sockets \* 1.6 GHz = 102.4 GB/s) Experiment Results : Achieved Bandwidth : 70 % ~75 % Effective bandwidth can be improved in the range of 10% to 15% with some optimizations

PARAM YUVA Node : Intel-R2208GZ; Intel Xeon E52670; Core Frequency : 2.6GHz; Cores per Node : 16 ; Peak Performance /Node : 2.35 TF; Memory : 64 GB;

| Data Size   | No. of Cores | Sustained Bandwidth |

|-------------|--------------|---------------------|

| (MegaBytes) | (OpenMP)     | (GB/sec)            |

| 1024        | 16           | 72.64               |

(\*) = Bandwidth results were gathered using untuned and unoptimized versions of benchmark (In-house developed) and Intel Prog. Env

**Source :** <u>http://www.intel.com</u>; Intel Xeon-Phi books, conferences, Web sites, Xeon-Phi Technical Reports <u>http://www.cdac.in/</u>

http://www.intel.in/content/dam/www/public/us/en/documents/perfo rmance-briefs/xeon-phi-product-family-performance-brief.pdf

## **Computing on Coprocessors : Think in Parallel**

## Performance = parallel hardware + scalable parallel prog.

Computing drives new applications

- Reducing "Time to Discovery"

- 100 x Speedup changes science & research methods

- New applications drive the future of Co-processors & GPUs

- Drives new GPU /Coprocessor capabilities

- > Drives hunger for more performance

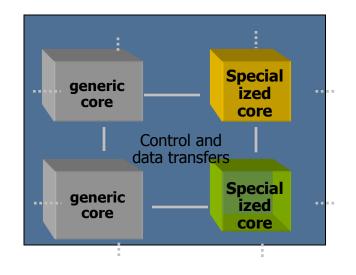

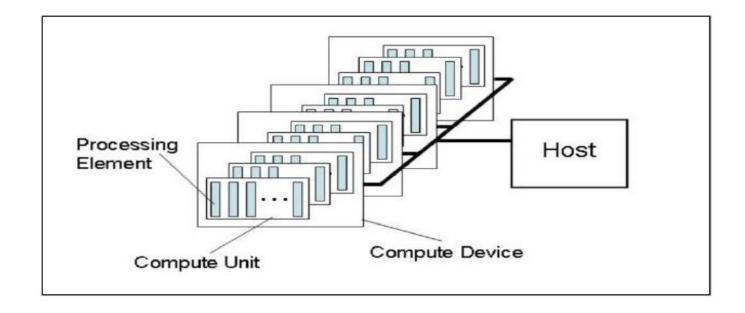

## **Systems with Accelerators**

A set (one or more) of very simple execution units that can perform few operations (with respect to standard CPU) with very high efficiency. When combined with full featured CPU (CISC or RISC) can accelerate the "nominal" speed of a system.

C-DAC hyPACK-2013

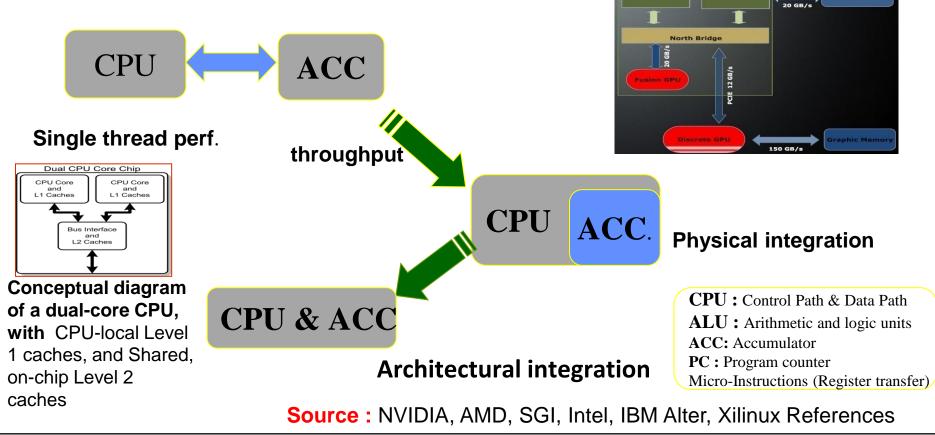

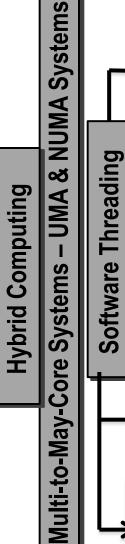

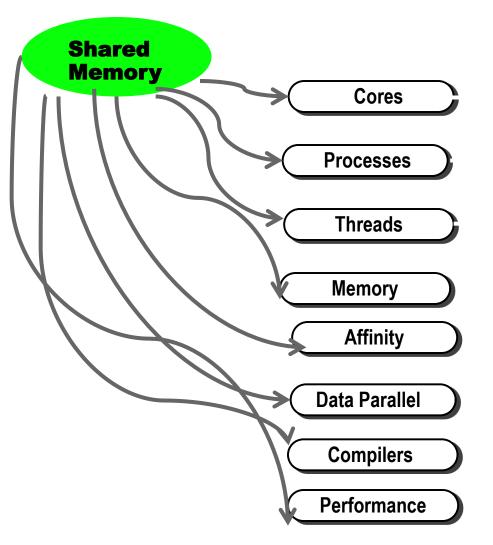

## Multi-Core Systems with Accelerator Types

- \* FPGA

- ≻ Xilinx, Alter

- \* GPU

- ➢ Nvidia (Kepler),

- > AMD Trinity APU

- \* MIC (Intel Xeon-Phi)

- Intel Xeon-Phi (MIC)

Source : NVIDIA, AMD, SGI, Intel, IBM Alter, Xilinux References

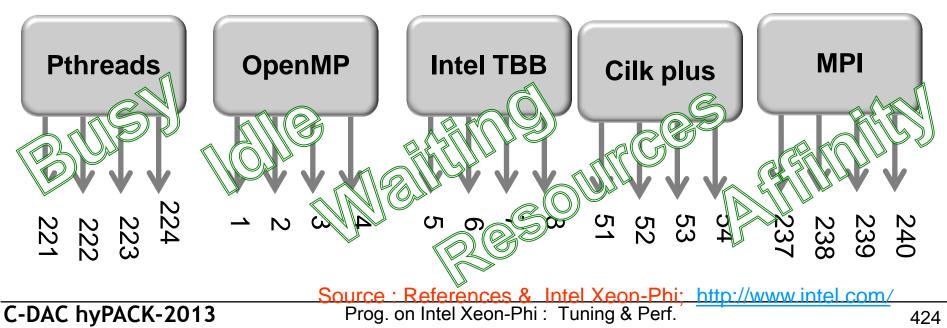

## **Prog.API - Multi-Core Systems with Devices**

C-DAC hyPACK-2013

## **Prog.API - Multi-Core Systems with Devices**

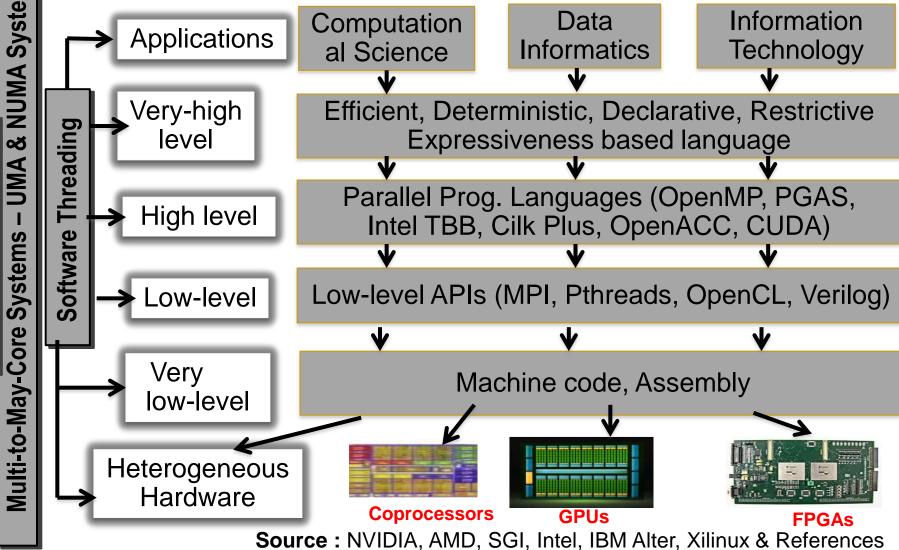

## **Typical UMA /NUMA Computing Systems**

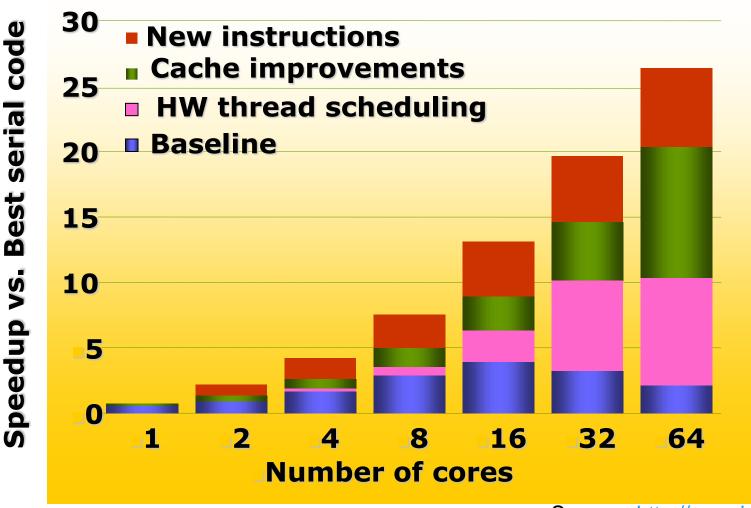

### System updates & Performance

#### Improvements

Quantify impacts prior to implementation

#### Small prototype available

What will be the performance of system ?

#### System available for measurement What will be performance for App

**Resources Availability** Application Scaling – Resources Available

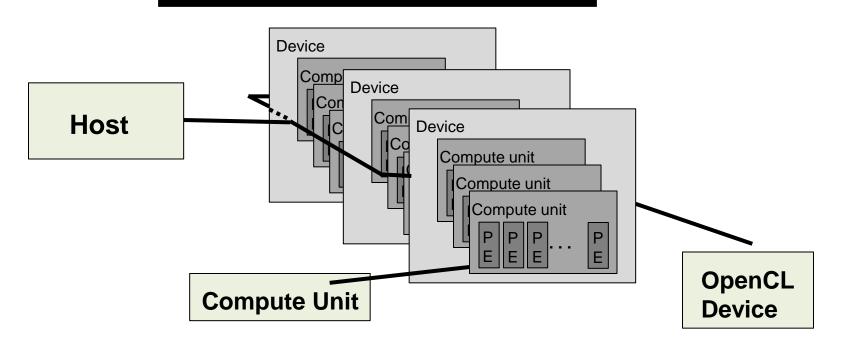

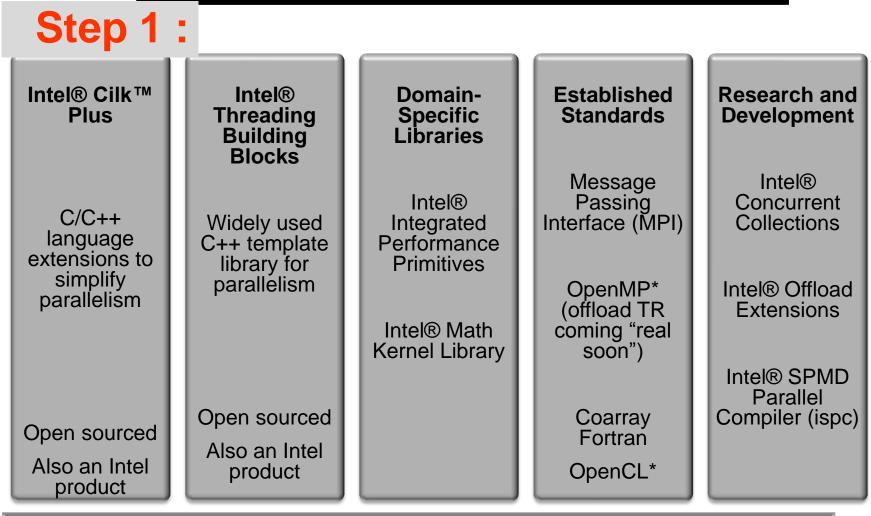

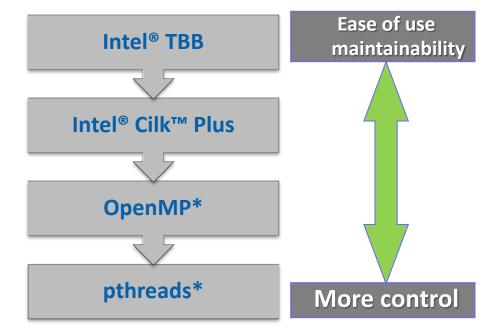

**High Level APIs :** HParallel Prog. Languages (OpenMP, PGAS, Intel TBB, Cilk Plus, OpenACC, CUDA)

**Low-level APIs :** MPI, Pthreads, OpenCL, FPGA-Verilog:

## **Prog.API - Multi-Core Systems with Devices**

## Intel Xeon Host : An Overview of Xeon - Multi-Core and Systems with Devices

# **Part-I** Xeon Phi Architecture & system Software

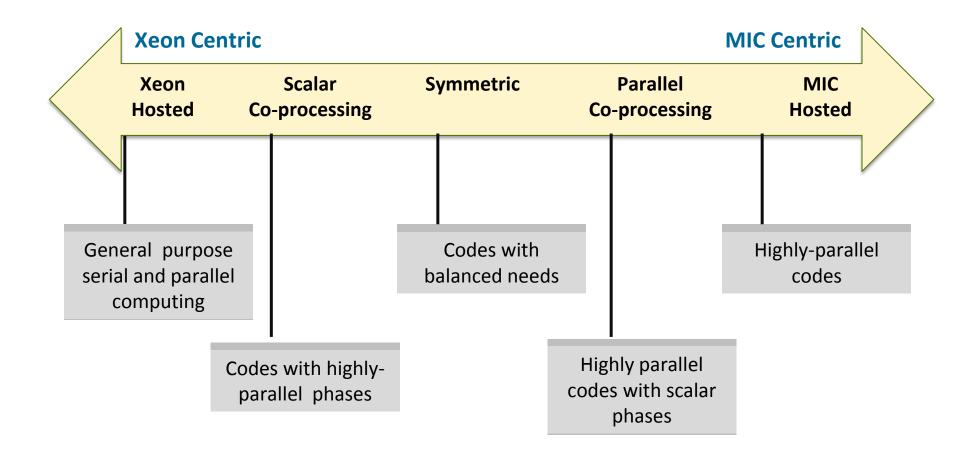

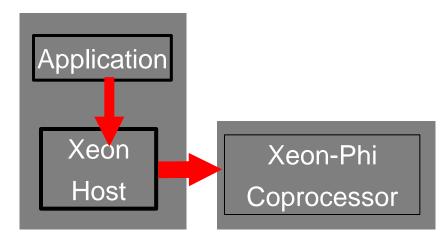

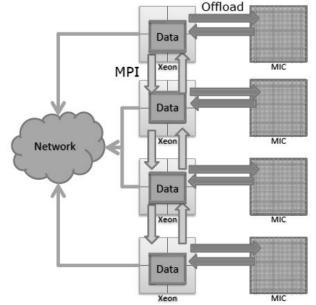

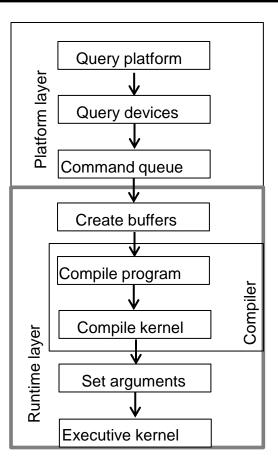

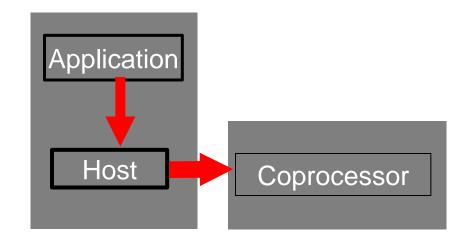

## **Prog.- Multi-Core Systems with Coprocessors**

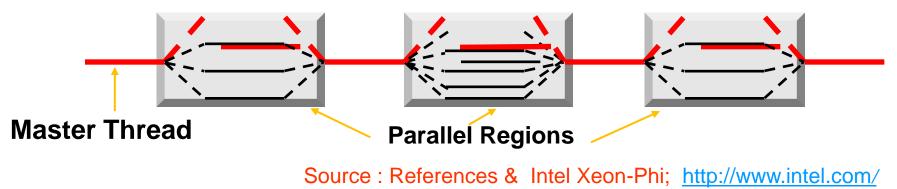

Source : References & Intel Xeon-Phi; http://www.intel.com/

C-DAC hyPACK-2013

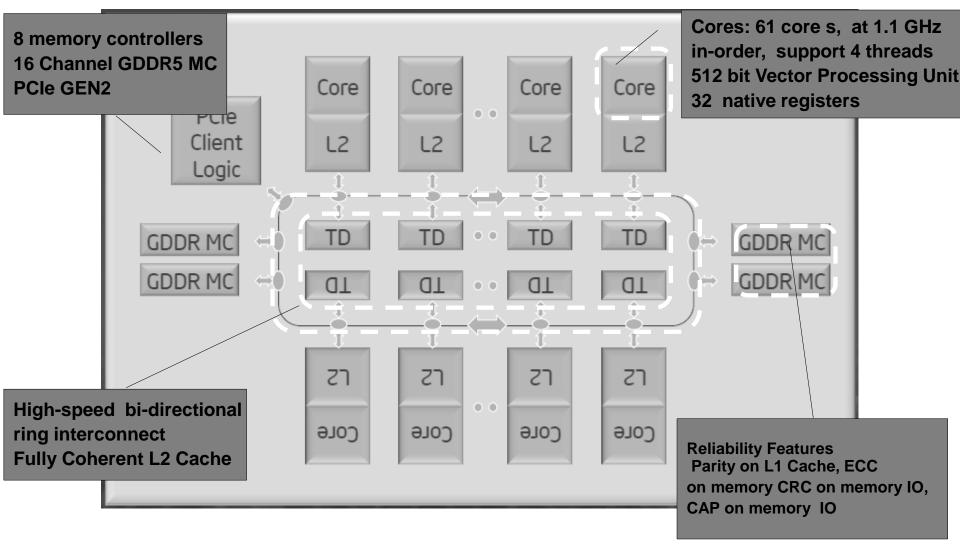

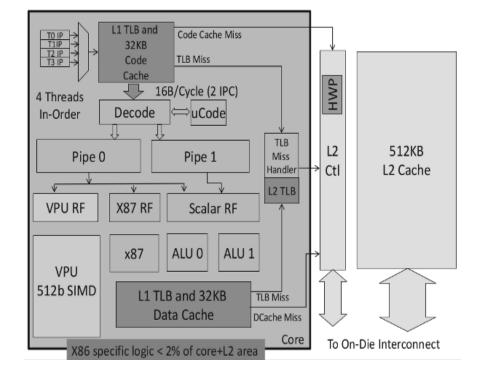

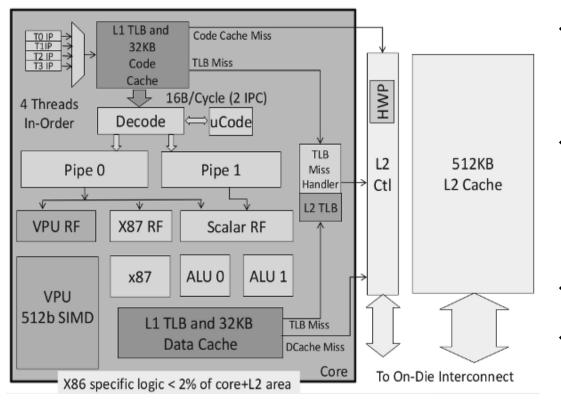

### Intel® Xeon Phi<sup>™</sup> Architecture Overview

Source : References & Intel Xeon-Phi; <u>http://www.intel.com/</u>

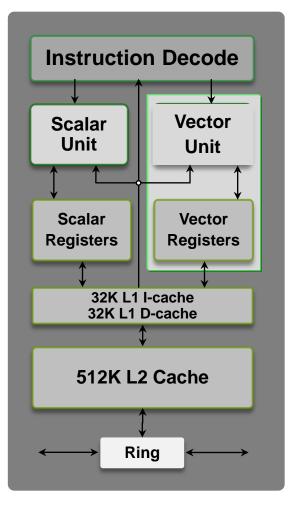

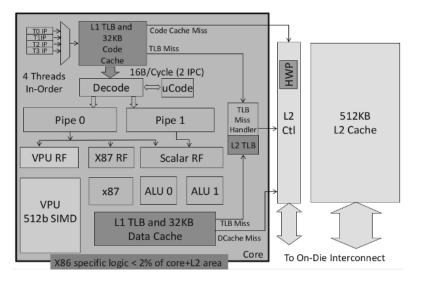

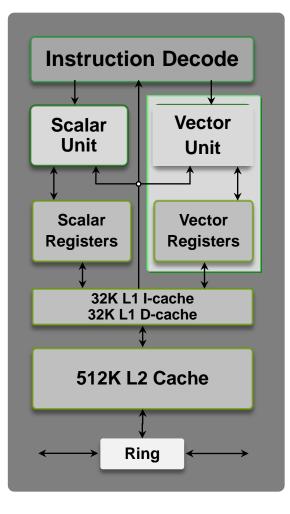

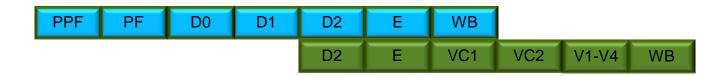

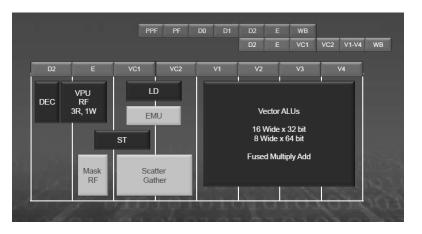

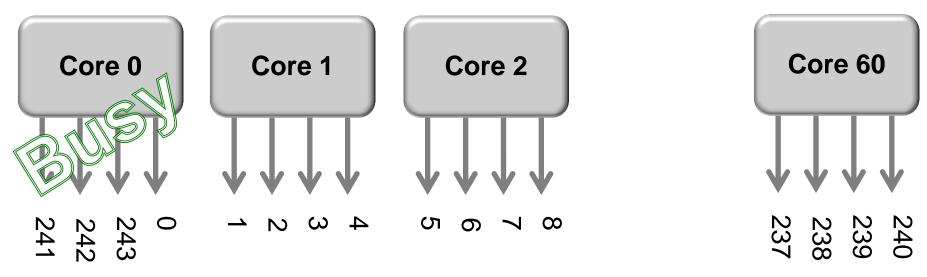

## Intel Xeon Phi Core Architecture Overview

- 60+ in-order, low power IA cores in a ring interconnect

- Two pipelines

- Scalar Unit based on Pentium<sup>®</sup> processors

- > Dual issue with scalar instructions

- Pipelined one-per-clock scalar throughput

- ✤ SIMD Vector Processing Engine

- ✤ 4 hardware threads per core

- 4 clock latency, hidden by round-robin scheduling of threads

- Cannot issue back to back inst in same thread

- ✤ Coherent 512KB L2 Cache per core

Source : References & Intel Xeon-Phi; http://www.intel.com/

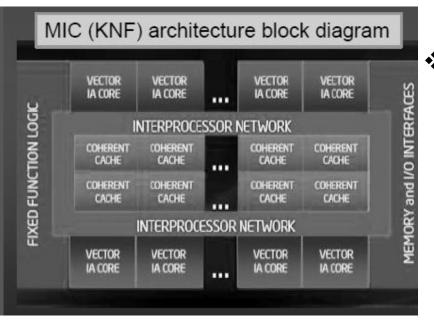

# MIC (Xeon Phi) Architecture

- MIC : Many Integrated Core

- Knight Corner co-processor

- Intel Xeon Phi co-processor

- > 22 nm technology

- > > 50 Intel Architecture cores

- connected by a high performance on-die bidirectional interconnect.

- > I/O Bus: PCle

- Memory Type: GDDR5 and >2x bandwidth of KNF

- Memory size: 8 GB GDDR5 memory technology

- > Peak performance: >1 TFLOP (DP)

- Single Linux image per chip

23

http://www.intel.com/

Source : References & Intel Xeon-Phi:

# (Xeon Phi Hardware)

- X16 PCIe 2.0 card in Xeon host system

- > Up to 60 cores, bi-directional ring bus

- > 1-2GB GDDR5 main memory

- CPU cores

- > 1.2GHz, 4-way threading

- > 512-bit SIMD vector unit

- > 32KB L1, 256KB L2

Source : References & Intel Xeon-Phi; http://www.intel.com/

- Xeon-Phi coprocessor capacity 8GB;

- processor :Xeon Phi 5110P; memory channel interface speed:

5.0 Giga Transfer/ Sec (GT/s); 8 memory controllers, each accessing two memory channels, used on co-processor

## **MIC Many Integrated Core Architecture**

### MIC Architecture

- Mnay cores on the die

- L1 and L2 cache

- Bidirectional ring network

- Memory and PCIe connection

### Knights Ferry-SW Dev Platform

- > Up to 32 cores

- > 1.2 GB of GDDRs RAM

- > 512-bit wide SIMD registers

- L1/L2 cahces

- Multiple threads (up to 4) per core

- Slow operation in double precision

## Xeon PHI (Was Knights Corener)

- Firsr product

- > Used in Stampede

- > 50+cores

- Increased amount of RAM

- Details are under NDA

- > 22nm technology

Source : References & Intel Xeon-Phi; <u>http://www.intel.com/</u>

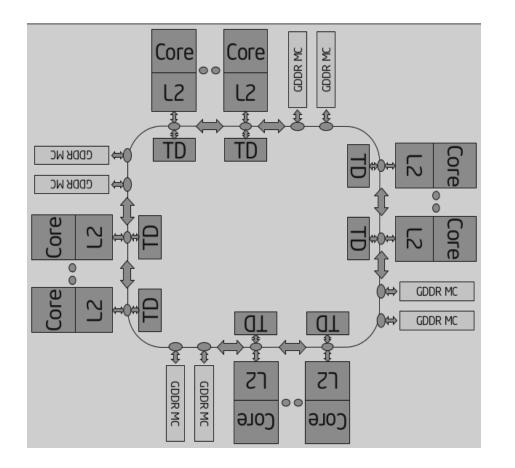

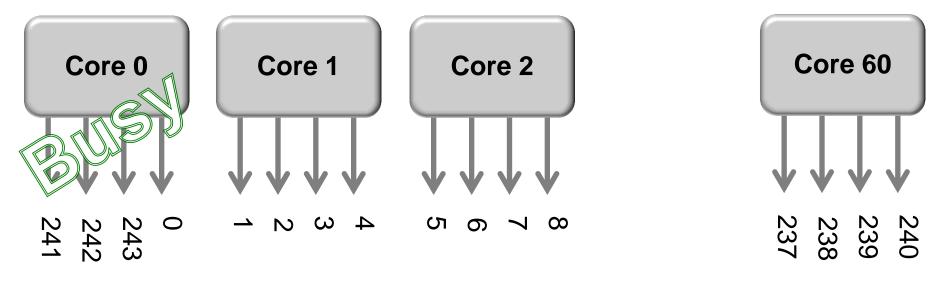

# MIC Intel Xeon Phi Ring

- Each microprocessor core is a fully functional, in-order core capable of running IA instructions independently of the other cores.

- Hardware multi-threaded cores

- Each core can concurrently run instructions from four processes or threads.

- The Ring Interconnect connecting all the components together on the chip

Source : References & Intel Xeon-Phi; http://www.intel.com/

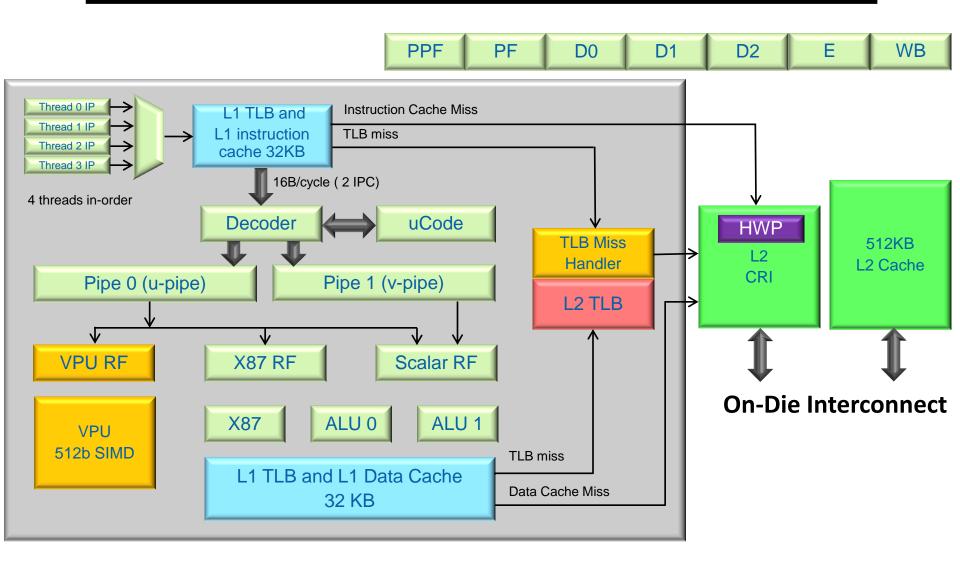

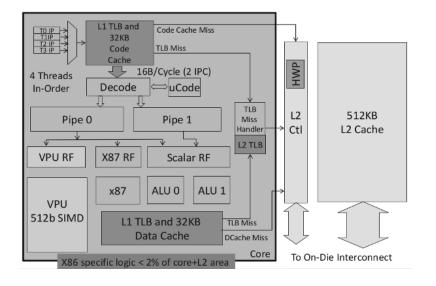

## The Processor Core

- Fetches and decodes instructions from four hardware thread execution contexts

- Executes the x86 ISA, and Knights Corner vector instructions

- The core can execute 2 instructions per clock cycle, one per pipe -32KB, 8-Way set associative L1 Icache & Dcache

- Core Ring Interface (CRI)

- L2 Cache

- Memory controllers (which access external memory devices to read and write data)

- PCI Express client: is the system interface to the host CPU or PCI Express switch,

Source : References & Intel Xeon-Phi; http://www.intel.com/

27

27

### Intel Xeon Phi : Coprocessor - Cache Overview

The L2 Cache

- Each core has a 512 KB L2 cache

- The L2 cache is part of the Core-Ring Interface block

- The L2 cache is private to the core: each core acts as a stand-alone core with 512 KB of total L2 cache space

- Other cores can not directly use them as a cache

- ♦ 512 KB x > 50 cores  $\rightarrow$  > 25 MB L2 on Knight Corner

- Tag Directory (**TD**) on each core, not private to the core

- A simplified way to view the many cores in Knights Corner is as a chip-level symmetric multiprocessor (SMP) and > 50 such cores share a high-speed interconnect on-die.

Source : References & Intel Xeon-Phi; <u>http://www.intel.com/</u>

28

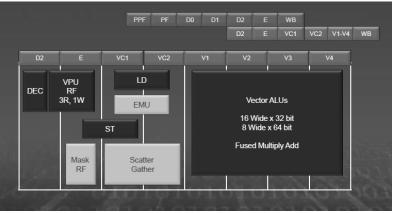

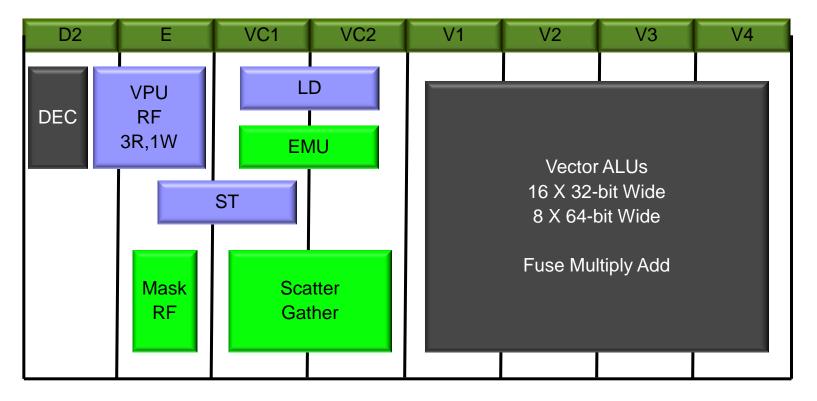

## The vector processing unit

- Vector processing unit (VPU) associated with each core.

- This is primarily a sixteenelement wide SIMD engine, operating on 512-bit vector registers.

- Gather / Scatter Unit

- Vector Mask

#### Source : References & Intel Xeon-Phi; http://www.intel.com/

## Xeon Phi : The Vector Processing Unit

- Vector processing unit (VPU) associated with each core.

- This is primarily a sixteen-element wide SIMD engine, operating on 512-bit vector registers.

- ✤ Gather / Scatter Unit

- Vector Mask

- Fetches and decodes instructions fr four hardware thread execution contexts

- Executes the x86 ISA, and Knights Corner vector instructions

- The core can execute 2 instructions per clock cycle, one per pipe - 32KB, 8-Way set associative L1 Icache & Dcache

- ✤ Core Ring Interface (CRI)

- ✤ L2 Cache

Source : References & Intel Xeon-Phi; <u>http://www.intel.com/</u>

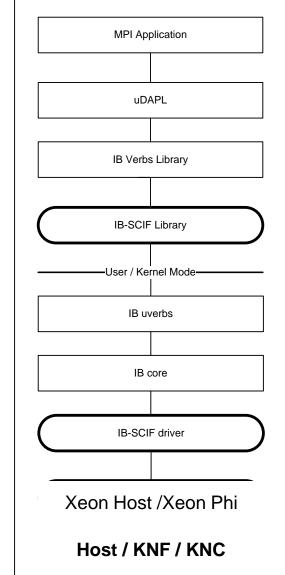

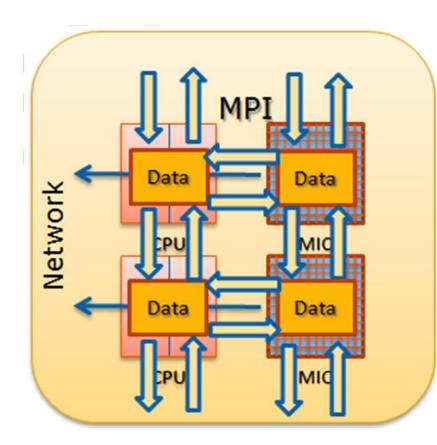

# Intel Xeon Phi - Software

- ✤ The System SW Stack

- Card OS

- > Symmetric Communications Interface (SCIF)

- Compiler Runtimes

- Coprocessor Offload Infrastructure (COI)

- Coprocessor Communication Link (CCL)

- > IB-SCIF

- MPI Dual-DAPL

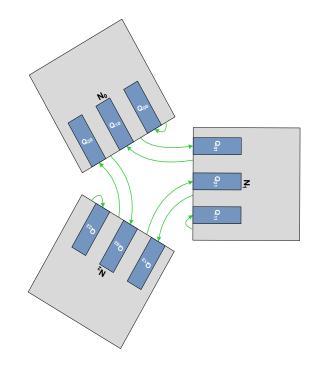

## Intel Xeon Phi : SCIF Introduction

- Primary goal: Simple, efficient communications interface between "nodes"

- ➤ Symmetric across Xeon host and Xeon Phi<sup>™</sup> Coprocessor cards

- User mode (ring 3) and kernel mode (ring 0) APIs

- Each has several mode specific functions

- Otherwise virtually identical

- Expose/leverage architectural capabilities to map host/card mapped memory and DMA engines

- Support a range of programming models

- Identical APIs on Linux and Windows

## Intel Xeon Phi : SCIF Introduction(2)

- Fully connected network of SCIF nodes

- Each SCIF node communicates directly with each other node through the PCIe root complex

- Nodes are physical endpoints in the network

- ➤ Xeon host and Xeon Phi<sup>™</sup> Coprocessor cards are SCIF nodes

- SCIF communication is *intra-platform*

- Key concepts:

- SCIF drivers communicate through dedicated queue pairs

- one "ring0 QP" for each pair of nodes

- A receive queue (Qij) in each node is directly written to from the other node.

- Interrupt driven, relatively low latency

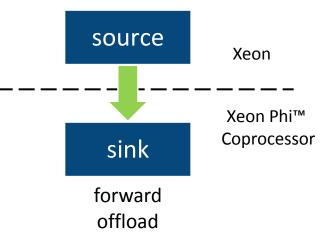

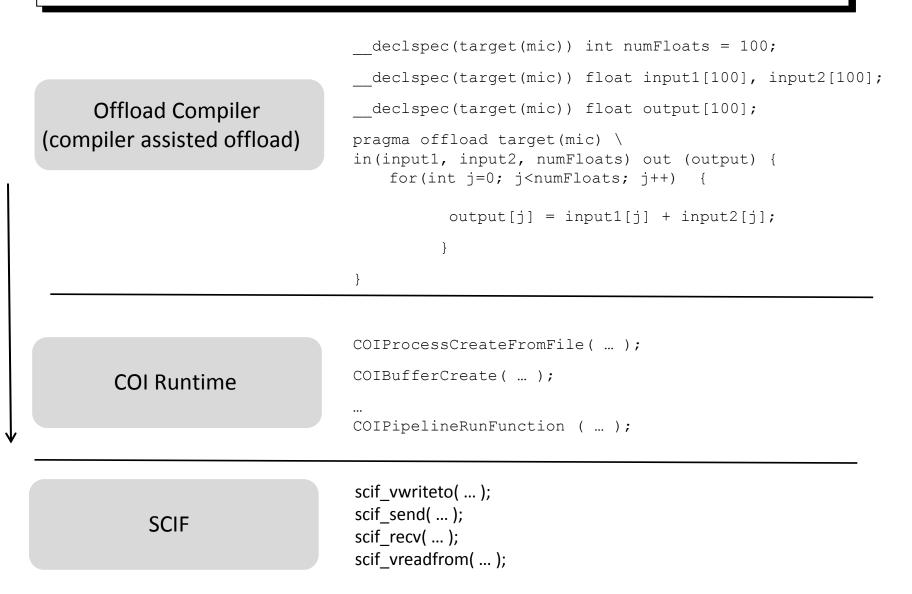

# A typical COI application is comprised of a source application and a sink offload *binary* The sink binary is a complete executable

The sink binary is a complete executable

**Coprocessor Offload Infrastructure (COI)**

- Not just a shared library

- Starts executing from main when it is loaded

"Source" is where "run functions" are initiated

"Sink" is where "run functions" are executed

- COI automatically loads dependent libraries prior to starting the offload binary on the sink

- COI has a *coi\_daemon* that spawns sink processes and waits for them to exit

\*\*

Intel Xeon Phi : COI Terminology

Commands are asynchronous function invocations ("run functions")

COI allows commands to be sent from a "source" to a "sink"

## Intel Xeon Phi : COI APIs

- COI exposes four major abstractions:

- > Use the simplest layer or add additional capabilities with more layers as needed

- > Each layer intended to interoperate with other available lower layers (e.g. SCIF)

- Enumeration: COIEngine, COISysInfo

- > Enumerate HW info; cards, APIC, cores, threads, caches, dynamic utilization

- Process Management: COIProcess (requires COIEngine)

- Create remote processes; loads code and libraries, start/stop

- Execution Flow: COIPipeline (requires COIProcess)

- > COIPipelines are the RPC-like mechanism for flow control and remote execution

- > Can pass up to 32K of data with local pointers

- Data and Dependency Management: COIBuffer, COIEvent (requires COIPipeline)

- > COIBuffers are the basic unit of data movement and dependence managment

- COIEvent optionally used to help manage dependences

- COIBuffers and COIEvents are typically used with Run Functions executing on COIPipelines

## Intel Xeon Phi : Coprocessor Communication Link (CCL)

## An Overview

- OFED is the industry standard code used for messaging on high-end HPC clusters

- > Supports Intel MPI and all open source MPIs

- $\succ$  Is in Linux and all the various Linux distributions

- RDMA over SCIF (IB-SCIF) RDMA within the platform between the host and KNC or multiple KNCs

- Intel

Xeon Phi ™ Coprocessor Communication Link (CCL) Direct

- ➢ Direct access to InfiniBand HCA from Intel® Xeon Phi ™

- Lowest latency data path

- - Pipeline data through host memory to InfiniBand network

- Higher bandwidth data path for some platform configurations

- ✤ Intel MPI dual-DAPL support

- Uses best data path, direct path for small messages, and proxy path for large messages for best overall MPI performance

Source : References & Intel Xeon-Phi; http://www.intel.com/

### Intel® Xeon Phi Coprocessor : CCL Direct Software

#### \* CCL-Direct

- ➤ Allows access to an HCA directly from the Xeon Phi<sup>™</sup> Coprocessor using standard OFED interfaces using PCI-E peer-to-peer transactions

- Provides the lowest latency data path

- > For each hardware HCA, a unique vendor driver has to be developed.

- e.g., mlx4, mthca, Intel® True Scale <sup>™</sup> hca etc

- Currently support for Mellanox HCAs (mlx4) exists and is shipping in MPSS

- Support for Intel® TrueScale<sup>™</sup> InfiniBand NICs via PSM is under development, expected release in early 2013

#### Implementation Limitations

- ➢ Intel® Xeon Phi<sup>™</sup> Coprocessor CCL Direct only supports user space clients, e.g. MPI

- Peak bandwidth is limited on some platforms and configurations

- CCL-Direct 1 byte latency is in the 2.5us range for Host-KNC, and 3.5-4us range for KNC-KNC across an InfiniBand HCA, peak BW varies depending on the Xeon platform

# Intel Xeon Phi : RDMA over IB-SCIF

- ◆OFED for Intel® Xeon Phi<sup>™</sup> Coprocessor uses the core OFA software modules from the Open Fabrics Alliance

- IB-SCIF is a new hardware specific driver and library that plugs into the OFED core mid-layer

- SCIF is the lowest level in the SW stack as we saw earlier

- ➢ Provides standard RDMA verbs interfaces within the platform, i.e., between the Intel® Xeon™ and Intel® Xeon Phi ™ Coprocessor cards within the same system.

- IBSCIF 1 byte latency is in the 13us range, (host-KNC), peak BW is in the 6GB/s per sec. range

#### Intel Xeon Phi Coprocessor – System SW Perspective

- ✤ Large SMP UMA machine a set of x86 cores to manage

- > 4 threads and 32KB L1I/D, 512KB L2 per core

- Supports loadable kernel modules we'll talk about one today

- Standard Linux kernel from kernel.org

- > 2.6.38 in the most recent release

- > Completely Fair Scheduler (CFS), VM subsystem, File I/O

- ♦ Virtual Ethernet driver— supports NFS mounts from Intel<sup>®</sup> Xeon Phi<sup>™</sup> Coprocessor

- New vector register state per thread for Intel<sup>®</sup> IMCI

- Supports "Device Not Available" for Lazy save/restore

- Different ABI uses vector registers for passing floats

- Still uses the x86\_64 ABI for non-float parameter passing (rdi, rsi, rdx ..)

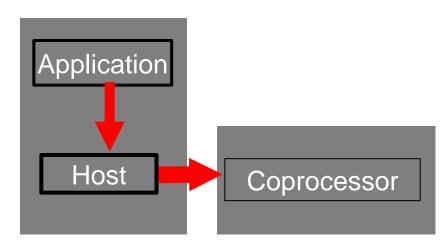

### Intel Xeon Phi : Coprocessor Offload Programming

# Xeon Phi : Programming Environment

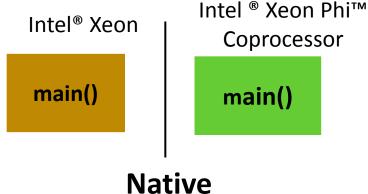

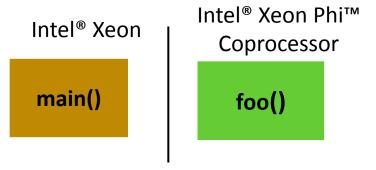

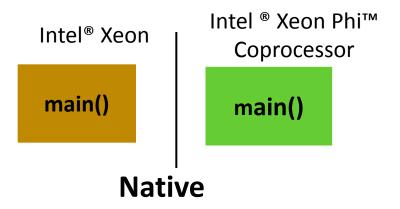

### **Execution Modes**

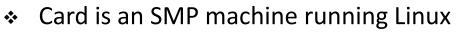

# Offload

- Card is an SMP machine running Linux

- Separate executables run on both MIC and Xeon

- e.g. Standalone MPI applications

- No source code modifications most of the time

- > Recompile code for Xeon Phi™ Coprocessor

- Autonomous Compute Node (ACN)

- "main" runs on Xeon

- Parts of code are offloaded to MIC

- Code that can be

- Multi-threaded, highly parallel

- Vectorizable

- Benefit from large memory BW

- Compiler Assisted vs. Automatic

- #pragma offload (...)

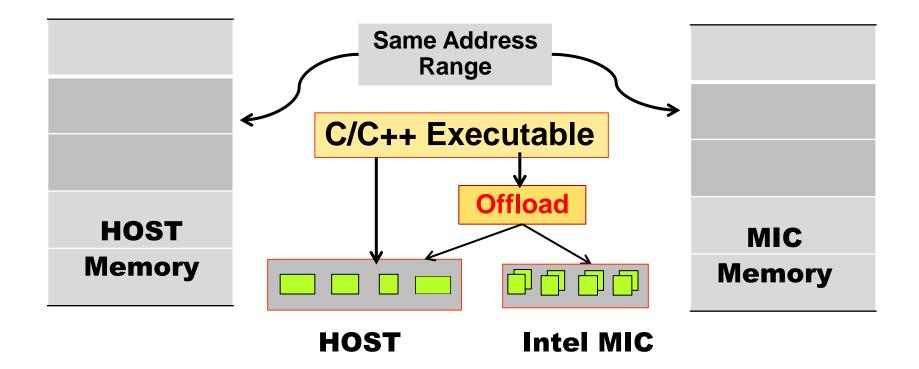

# Xeon Phi : Programming Environment

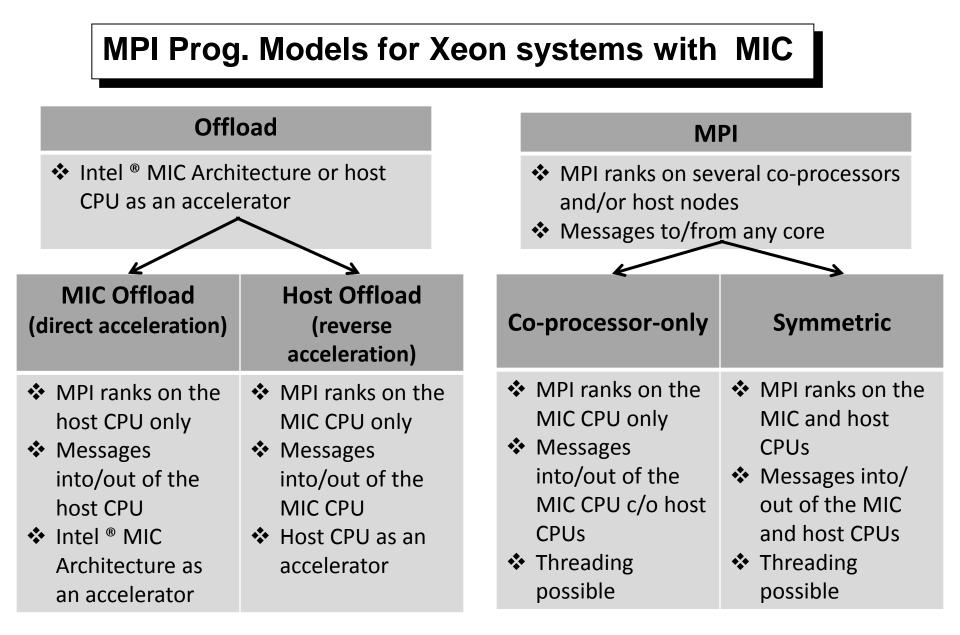

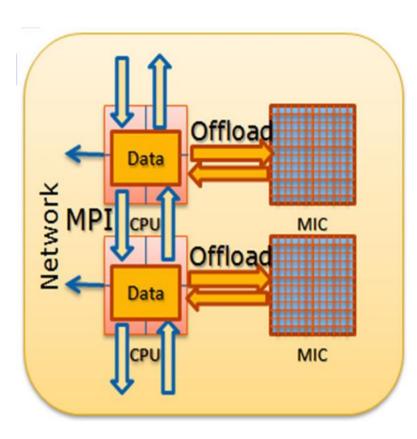

#### **Execution Modes**

Shared Address Space Programming (Offload, Native, Host)

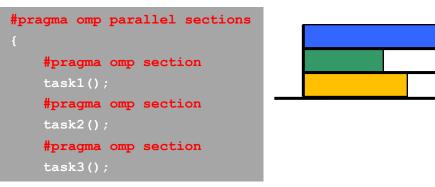

OpenMP, Inetl TBB, Cilk Plus, Pthreads

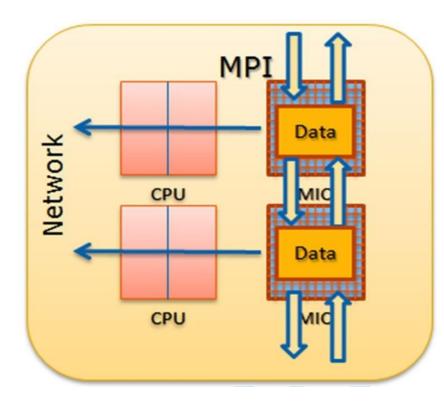

Message Passing Programming (Offload – MIC Offload /Host Offload) (Symmetric & Coprocessor /Host)

# Hybrid Programming (MPI – OpenMP, MPI Cilk Plus MPI-Intel TBB)

# **Xeon Phi : Data Access Semantics**

### Data Access Semantics

- ➤Explicit Offloading

- Implicit Offloading

- Complier Data Transfer Overview

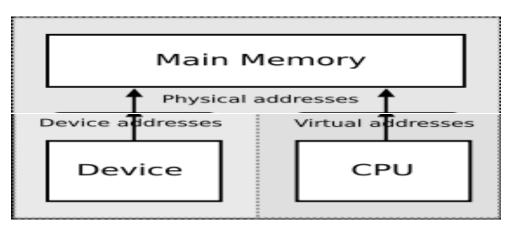

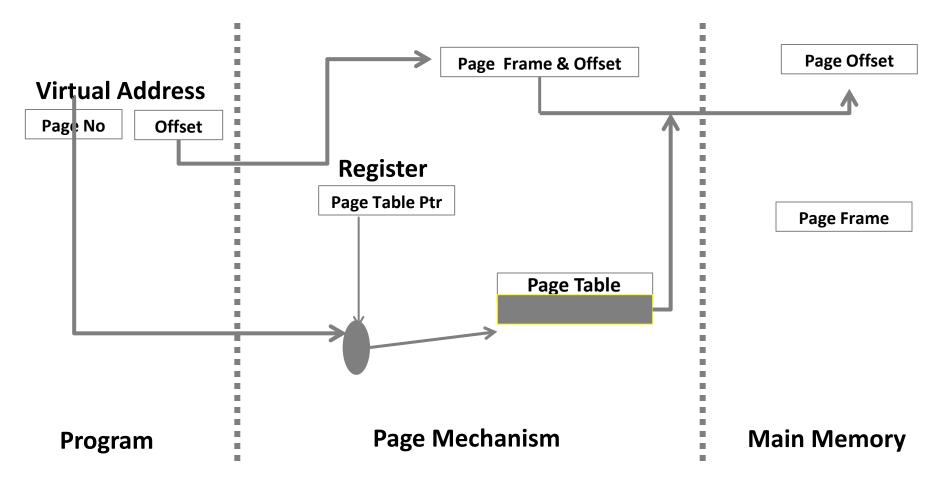

- The host CPU and the Intel Xeon Phi coprocessor do not share physical or virtual memory in hardware

# Two offload transfer models are : Explicit Copy and Implicit Copy

# Xeon Phi : Data Access Semantics

- Two offload transfer models are : Explicit Copy and Implicit Copy

- **\*** Explicit Copy :

- Programmer designates variables that need to be copied between host and card in the offload directive

- **Syntax:** Pragma/directive-based

- C/C++ Example: #pragma offload target(mic) in(data:length(size)) (OpenMP, Pthreads, Intel TBB, MPI with OpenMP/Pthreads/Intel TBB)

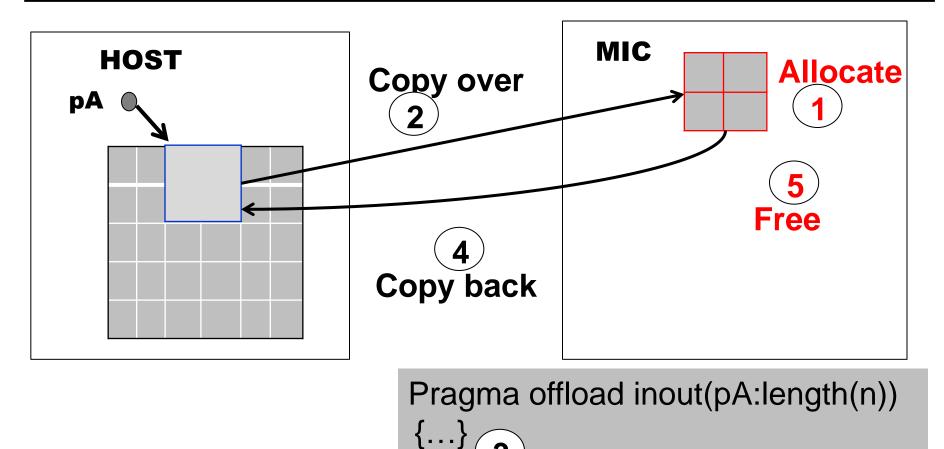

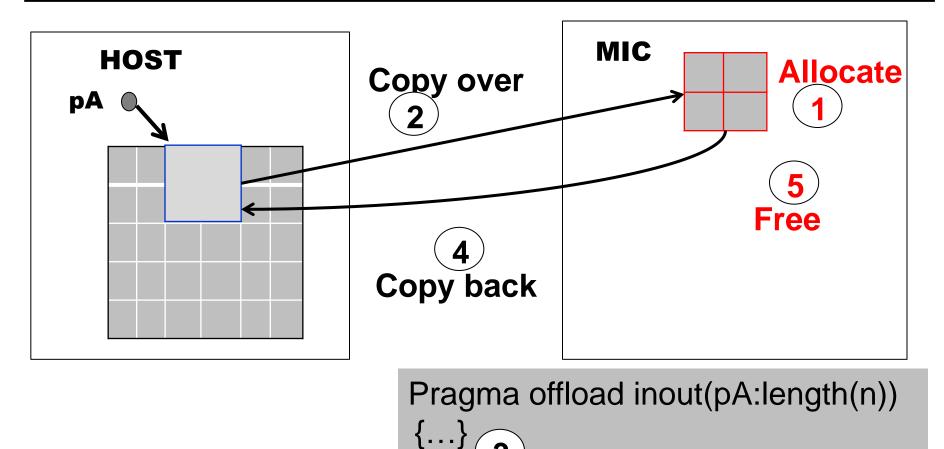

# **Compiler : Offload using Explicit Copies – Data movement**

Default treatment of in/out variables in a #pragma offload statement

# **Compiler : Offload using Explicit Copies – Data movement**

- Default treatment of in/out variables in a #pragma offload statement

- At the start of an offload:

- Space is allocated on the coprocessor

- **in** variables are transferred to the coprocessor

- ➤ At the end of an offload:

- **out** variables are transferred from the coprocessor

- Space for both types (as well as **inout**) is **deallocated** on the coprocessor

# Compiler : Offload using Explicit Copies

|                                                        | C/CC+ Syntax                                                                      | Semantics                                                                               |  |

|--------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|

| Offload pragma                                         | <pre>#pragma offload <clauses>   <statement block=""></statement></clauses></pre> | Allow next statement block to<br>execute on Intel MIC Arch or<br>host CPU               |  |

| Keyword for<br>variable & function<br>definitions      | _attribute_((target(mic)))                                                        | Compile for, or allocate variable on, both CPU and Intel MIC Arch.                      |  |

| Entire Blocks of<br>Code                               | <pre>#pragma offload_attribute(push, target(mic))</pre>                           | Mark entire files or large<br>blocks of code for generation<br>on both host CPU         |  |

| Data Transfer #pragma offload_transfer<br>target(mic)  |                                                                                   | Initiates asynchronous data<br>transfer, or initiates and<br>completes synchronous data |  |

| Synchronization#pragma offload_waitsignal(signal_slot) |                                                                                   | Wait asynchronous offload processes to complete                                         |  |

# Compiler : Offload using Explicit Copies

|                                                 | Fortran                                                                                      | Semantics                                                                               |

|-------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Offload directive                               | Offload directive<br>!dir\$ omp offload <clause><br/><openmp construct=""></openmp></clause> | Execute next<br>OpenMP* parallel construct<br>on Intel <sup>®</sup> MIC Architecture    |

|                                                 | !dir\$ offload <clauses><br/><statement></statement></clauses>                               | Execute next statement<br>(function call) on Intel <sup>®</sup> MIC<br>Architecture     |

| Keyword for<br>variable/function<br>definitions | !dir\$ attributes<br>offload: <mic> :: <rtn-name></rtn-name></mic>                           | Compile function or variable<br>for CPU and Intel <sup>®</sup> MIC<br>Architecture      |

| Data Transfer                                   | <pre>#pragma offload_transfer target(mic)</pre>                                              | Initiates asynchronous data<br>transfer, or initiates and<br>completes synchronous data |

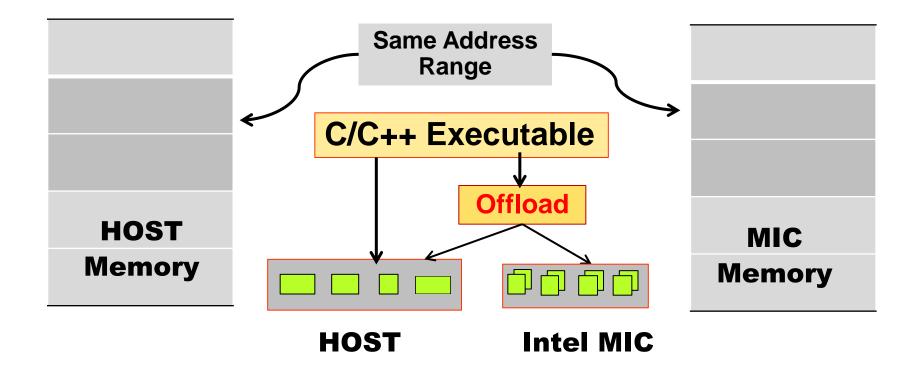

# **Xeon Phi : Data Access Semantics**

### Data Access Semantics

Implicit Offloading

- Section of memory maintained at the same virtual address on both the host and Intel MIC Architecture coprocessor

- Reserving same address range on both devices allows

- Seamless sharing of complex pointer-containing data structures

- Elimination of user marshaling and data management

- Use of simple language extensions to C/C++

# **Compiler : Offload using Explicit Copies – Data movement**

# **Heterogeneous Compiler : Offload using Implicit Copies**

#### When "shared" memory is synchronized

- Automatically done around offloads (so memory is only synchronized on entry to, or exit from, an offload call)

- Only modified data is transferred between CPU and coprocessor

- Dynamic memory you wish to share must be allocated with special functions: \_Offload\_shared\_malloc,

\_Offload\_shared\_aligned\_malloc, \_Offload\_shared\_free, \_Offload\_shared\_aligned\_free

- Allows transfer of C++ objects

- Pointers are no longer an issue when they point to "shared" data

- Well-known methods can be used to synchronize access to shared data and prevent data races within offloaded code

– E.g., locks, critical sections, etc.

This model is integrated with the Intel Cilk Plus Parallel Extensions Supported in C /C++ Languages Only

# **Compiler : Data Transfer Overview Compiler**

- Two offload transfer models are : Explicit Copy and Implicit Copy

- Implicit Copy :

- Programmer makes variables that need to be shared between **host** and **mic** card

- The same variable can be used in both host and coprocessor code

- Runtime automatically maintains coherence at the beginning and end of offload statements

- Syntax: keyword extensions based

- Example: \_Cilk\_shared double foo;

Offload func(y);

Intel Xeon Phi Coprocessors :

**Compilation and Vectorization**

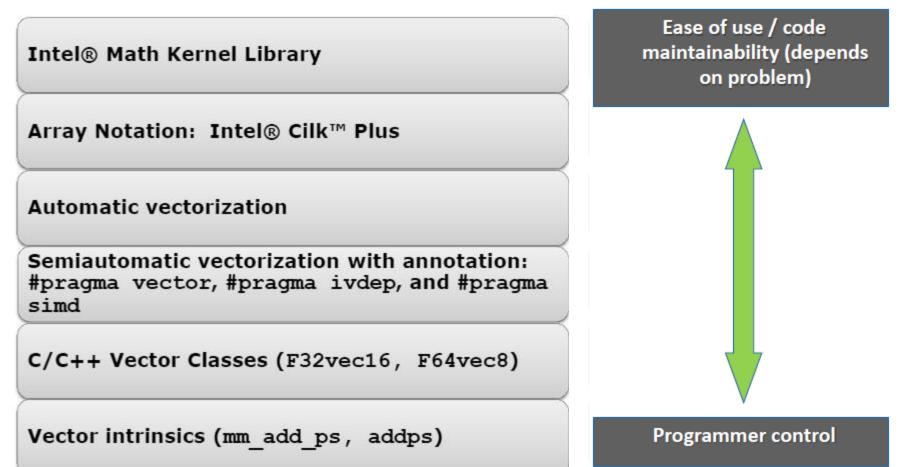

# **Part-2** Vectorization Methodlogy

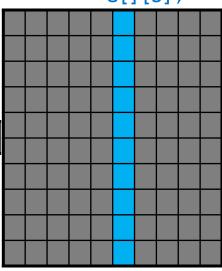

**Vectorization** is the process of converting an algorithm from a **scalar** implementation to a **vector process**.

Scalar : an operation one pair of operands at a time

**Vector :** A process in which a single instruction can refer to a vector (series of adjacent values)

- it adds a form of parallelism to software in which one instruction or operation is applied to multiple pieces of data.

- Efficient Processing of Data Movement is required to get improvement in performance.

- Many general-purpose microprocessors support SIMD (single-instruction-multiple-data) parallelism

- When the hardware is coupled with C/ C++ compilers that support it, developers have an easier time delivering more efficient, better performing software

- Types of Vector Computations in Applications

Multi-media Applications

- Scientific and Engineering Applications

- Graphic Computations

- Computational Finance

- Information Science Applications

# Compilers :

- Performance or efficiency benefits from vectorization depend on the code structure.

- Automatic & near automatic techniques (Auto-Vectorization feature) introduced below are most productive in delivering improved performance or efficiency.

# SIMD Support

➤Intel C++ Compilers

≻Intel Fortran 90 Compilers

Compliers supporting SIMD Instructions

Intel Compilers supporting the Intel Streaming SIMD Extensions (Intel SSE) & Intel Advanced Vector Extensions (Intel AVX) on both IA-32 and Intel 64 processors.

# **Compilers** :

- Auto-vectorization : Performance or efficiency benefits from vectorization depend on the both compilers do autovectorization, generating Intel SIMD code to automatically vectorize parts of application software when certain conditions are met.

- Portability Problems : Because no source code changes are required to use auto-vectorization, there is no impact on the portability of your application.

- To take advantage of auto-vectorization, applications must be built at default optimization settings (-O2) or higher. No additional or special switch setting is needed using packed SIMD instructions

# Advantage of Intel MKL and Intel IPP

- Intel Math Kernel Library (MKL)

- Intel® Integrated Performance Primitives (IPP) is another library for C and C++ developers,

- Another easy way to take advantage of vectorization is to make calls in your applications to the vectorized forms of functions in the Intel® Math Kernel Library. Much of Intel MKL is threaded and supports auto-vectorization to help you get the most of today's multi-core processors. Intel MKL functions are also fully thread-safe, so multiple calls for different threads will not conflict with one another.

- Intel IPP offers libraries that can be called for multimedia, data processing, and communications applications

Whenever possible, instructions on data arrays are processed in an assembly line manner, where several pieces of data are undergoing different parts of an operation simultaneously

#### **Vector Registers**

The vector computers get most of their speed through vector operations. This means that a single type of instruction on multiple data. This is uniquely accomplished through the use of vector registers.

#### **Vector Chaining**

Vector chaining is a way to decrease vector start-up time. On the C90 a functional unit can begin processing data as soon as the first elements are in the registers.

#### About Vectorization :

High performance is dependent on the vectorization of long loops. Poor performance can result from the inhibition of this vectorization.

#### Types of Computation in Applications

- Loop Not Innermost

- Vector Dependencies

- Other Not Vectorizable Constructs

- Memory Conflicts

- > I/O Optimization

#### Loop No nnermost

#### Problem

- Only innermost loop can be vectorized at the machine instruction level. However, it may be more efficient to vectorize the operations in the outer loops instead. This could be the case if:

- The inner loop is inhibited from vectorization

- > The outer loop has a longer vector length than the inner loop

- The outer loop does more work than the inner loop

#### Solution

- The solution is to make the outer loop innermost. Depending on the structure of the loops, there are three ways to do this:

- Swap the loops

- Split the outer loop

- Unwind the inner loop

#### **Vector Dependencies**

**Problem :** Dependencies occur when each iteration of a loop is dependent on the result of previous iterations.

- There are three kinds of dependency:

- (1) Result not ready (recurrence or recursion)

- (2) Value destroyed (3) Ambiguous subscript

#### Solution :

#### **Result Not Ready**

- The solution is to restructure the loop to remove the dependency. Sometimes, this is difficult and requires rethinking the algorithm. Often, however, you can do it by:

- Swapping loops **OR** Splitting the dependent work out of the loop

#### Value Destroyed

You generally do not have to worry about this kind of dependency. The compiler handles it by saving the values in a temporary array.

#### **Ambiguous Subscript**

The solution is to use an IVDEP directive to tell the compiler that there is not dependency (if that is in fact the case!)

C-DAC hyPACK-2013 Xeon-Phi Coprocessors : An Overview

# **Other Non-vectorizable Constructs**

#### Problem

- There are a number of other constructs that prevent vectorization. These include:

- I/O statements (These generate calls no library subroutines)

- CHARACTER data and functions

- STOP and PAUSE

- Assigned GOTO (obsolete, anyway)

#### Solution

The only solution is to move these constructs out of the loop, either by splitting or by recording so that the constructs are unnecessary

# **Typical Vector Computer Features**

- Fast Clock Speed.

- Segmented, Vector Functional Units

- Independent Functional Units

- Register-to-Register Operations

- Shared, Banked Memory

- No Virtual Memory Fast I/O

# **Vectorization and SIMD Execution**

SIMD

- Flynn's Taxonomy: Single Instruction, Multiple Data

- CPU perform the same operation on multiple data elements

SISD

- Single Instruction, Single Data

- Vectorization

- In the context of Intel® Architecture Processors, the process of transforming a scalar operation (SISD), that acts on a single data element to the vector operation that that act on multiple data elements at once(SIMD).

- Assuming that setup code does not tip the balance, this can result in more compact and efficient generated code

- For loops in "normal" or "unvectorized" code, each assembly instruction deals with the data from only a single loop iteration

# Intel Xeon Phi : Vector Unit

# **Understand floating point arithmetic Unit**

- Vector Processing Unit executing vector FP instruction

- ✤ X87 unit also exist can execute FP Instruction as well

- ✤ Compiler choose which place to use for FP operation

- ✤ VPU is preferred place because of its speed

- > VPU can make the FP results reproducible as well

- Use X87 should be used for two reasons

- > Reproduce the same results 15 years ago, right or wrong

- Need generate FP exceptions for debugging purpose

- Intel Compiler default to VPU the user can override with

-fp-model strict

- Vectorized, high precision of division, square root and transcendental functions from libsvml

-fp-model-precise -no-prec-div -no-prec-sqrt -

fast-transcendentals -fimf-precision=high

### **Core Architecture Overview**

- 60+ in-order, low power IA cores in a ring interconnect

- Two pipelines

- Scalar Unit based on Pentium<sup>®</sup> processors

- > Dual issue with scalar instructions

- > Pipelined one-per-clock scalar throughput

- ✤ SIMD Vector Processing Engine

- ✤ 4 hardware threads per core

- > 4 clock latency, hidden by round-robin scheduling of threads

- Cannot issue back to back inst in same thread

- ✤ Coherent 512KB L2 Cache per core

# **Vector Processing Unit Extends the Scalar IA Core**

Source : References & Intel Xeon-Phi; http://www.intel.com/

C-DAC hyPACK-2013

Xeon-Phi Coprocessors : An Overview

# **Core extension Vector Processing Unit**

Source : References & Intel Xeon-Phi; http://www.intel.com/

C-DAC hyPACK-2013

Xeon-Phi Coprocessors : An Overview

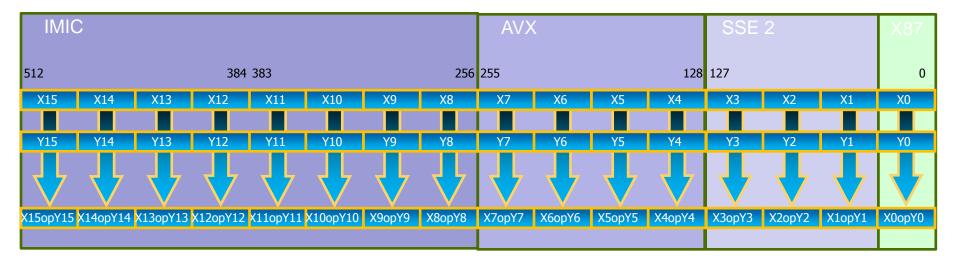

# **Vector Processing Unit and Intel® IMCI**

- Vector Processing Unit Execute Intel<sup>®</sup> IMCI

- > Intel<sup>®</sup> Initial Many Core Instructions

- ✤ 512-bit Vector Execution Engine

- > 16 lanes of 32-bit single precision and integer operations

- > 8 lanes of 64-bit double precision and integer operations

- > 32 512-bit general purpose vector registers in 4 thread

- > 8 16-bit mask registers in 4 thread for predicated execution

- ✤ Read/Write

- > One vector length (512-bits) per cycle from/to Vector Registers

- > One operand can be from the memory free

- ✤ IEEE 754 Standard Compliance

- > 4 rounding Model, even, 0, + $\infty$ , - $\infty$

- > Hardware support for SP/DP denormal handling

- Sets status register VXCSR flags but not hardware traps

# Xeon Phi : The Vector Processing Unit

- Vector processing unit (VPU) associated with each core.

- This is primarily a sixteen-element wide SIMD engine, operating on 512-bit vector registers.

- ✤ Gather / Scatter Unit

- Vector Mask

- Fetches and decodes instructions fr four hardware thread execution contexts

- Executes the x86 ISA, and Knights Corner vector instructions

- The core can execute 2 instructions per clock cycle, one per pipe - 32KB, 8-Way set associative L1 Icache & Dcache

- ✤ Core Ring Interface (CRI)

- L2 Cache

### Intel Xeon Phi : Vector Instruction Performance

#### **Vector processing**

| do i = 1, N      |  |

|------------------|--|

| A(i) = B(i)+C(i) |  |

| end do           |  |

$V0 \leftarrow V1 + V2$

| CP 0 | B(3) B(2) B(1)<br>C(3) C(2) C(1)   |                                                                                                                                                       |

|------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| CP 1 | B(4) B(3) B(2)<br>C(4) C(3) C(2)   | B(1)<br>C(1)                                                                                                                                          |

| CP 2 | B(5) B(4) B(3)<br>C(5) C(4) C(3)   | B(2) B(1)<br>C(2) C(1)                                                                                                                                |

| CP 3 | B(6) B(5) B(4)<br>C(6) C(5) C(4)   | B(3)         B(2)         B(1)           C(3)         C(2)         C(1)                                                                               |

| CP 4 | B(7) B(6) B(5)<br>C(7) C(6) C(5)   | B(4)         B(3)         B(2)         B(1)           C(4)         C(3)         C(2)         C(1)                                                     |

| CP 5 | B(8) B(7) B(6)<br>C(8) C(7) C(6)   | B(5)         B(4)         B(3)         B(2)         B(1)           C(5)         C(4)         C(3)         C(2)         C(1)                           |

| CP 6 | B(9) B(8) B(7)<br>C(9) C(8) C(7)   | B(6)         B(5)         B(4)         B(3)         B(2)         B(1)           C(6)         C(5)         C(4)         C(3)         C(2)         C(1) |

| CP 7 | B(10) B(9) B(8)<br>C(10) C(9) C(8) | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                 |

**Functional Unit Add Floating Point**

#### Source : References & Intel Xeon-Phi; http://www.intel.com/

C-DAC hyPACK-2013

Xeon-Phi Coprocessors : An Overview

#### Intel Xeon Phi : Vector Instruction Performance

- ✤ VPU contains 16 SP ALUs, 8 DP ALUs,

- Most VPU instructions have a latency of 4 cycles and TPT 1 cycle

- Load/Store/Scatter have 7-cycle latency

- Convert/Shuffle have 6-cycle latency

- VPU instruction are issued in u-pipe

- Certain instructions can go to v-pipe also

- Vector Mask, Vector Store, Vector Packstore, Vector Prefetch, Scalar

#### Intel Xeon Phi : Vector Instruction Performance

- Vectorization is key for performance

- Sandybridge, MIC, etc.

- ➤Compiler hints

- Code restructuring

- Many-core nodes present scalability challenges

- Memory contention

- Memory size limitations

#### **Demand vectorization by annotation - #pragma simd**

- \$ Syntax: #pragma simd [<clause-list>]

- Mechanism to force vectorization of a loop

- Programmer: asserts a loop ought to be vectorized

- Compiler: vectorizes the loop or gives an error

| Clause                                                                               | Semantics                                                                                                                                 |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| No clause                                                                            | Enforce vectorization of innermost loops; ignore dependencies etc                                                                         |

| vectorlength ( <i>n<sub>1</sub>[, n<sub>2</sub>]</i> )                               | Select one or more vector lengths (range: 2, 4, 8, 16) for the vectorizer to use.                                                         |

| private <b>(var<sub>1</sub>, var<sub>2</sub>,, var<sub>N</sub>)</b>                  | Scalars private to each iteration. Initial value broadcast to all instances. Last value copied out from the last loop iteration instance. |

| linear (var <sub>1</sub> :step <sub>1</sub> ,, var <sub>N</sub> :step <sub>N</sub> ) | Declare induction variables and corresponding positive integer step sizes (in multiples of vector length)                                 |

| reduction <i>(operator:var<sub>1</sub>, var<sub>2</sub>,, var<sub>N</sub>)</i>       | Declare the private scalars to be combined at the end of the loop using the specified reduction operator                                  |

| [no]assert                                                                           | Direct compiler to assert when the vectorization fails. Default is to assert for SIMD pragma.                                             |

| Source                                                                               | : References & Intel Xeon-Phi; <u>http://www.intel.com/</u>                                                                               |

#### SIMD Abstraction – Vectorization/SIMD

| <pre>for (i = 0; i &lt; 15; i++) if (v5[i] &lt; v6[i])</pre> | SIMD can simplify your code and reduce the jumps, breaks in program flow control |

|--------------------------------------------------------------|----------------------------------------------------------------------------------|

| v1[i] += v3[i];                                              | Note the lack of jumps or conditional code branches                              |

| <b>v</b> 5 | =   | 0   | 4   | 7     | 8    | 3   | 9   | 2   | 0  | 6 | 3 | 8 | 9 | 4 | 5 | 0 | 1 |

|------------|-----|-----|-----|-------|------|-----|-----|-----|----|---|---|---|---|---|---|---|---|

| <b>v6</b>  | =   | 9   | 4   | 8     | 2    | 0   | 9   | 4   | 5  | 5 | 3 | 4 | 6 | 9 | 1 | 3 | 0 |

| VCI        | npp | oi_ | _11 | t ]   | c7 , | , ٦ | 75, | ۲ ، | 76 |   |   |   |   |   |   |   |   |

| k7         | =   | 1   | 0   | 1     | 0    | 0   | 0   | 1   | 1  | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

|            |     |     |     |       |      |     |     |     |    |   |   |   |   |   |   |   |   |

| <b>v</b> 3 | =   | 5   | 6   | 7     | 8    | 5   | 6   | 7   | 8  | 5 | 6 | 7 | 8 | 5 | 6 | 7 | 8 |

| <b>v</b> 1 | =   | 1   | 1   | 1     | 1    | 1   | 1   | 1   | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| vac        | ldr | bi  | v]  | L { ] | c7]  | },  | v1  | ,   | v3 | 3 |   |   |   |   |   |   |   |

| <b>v</b> 1 | =   | 6   | 1   | 8     | 1    | 1   | 1   | 8   | 9  | 1 | 1 | 1 | 1 | 6 | 1 | 8 | 1 |

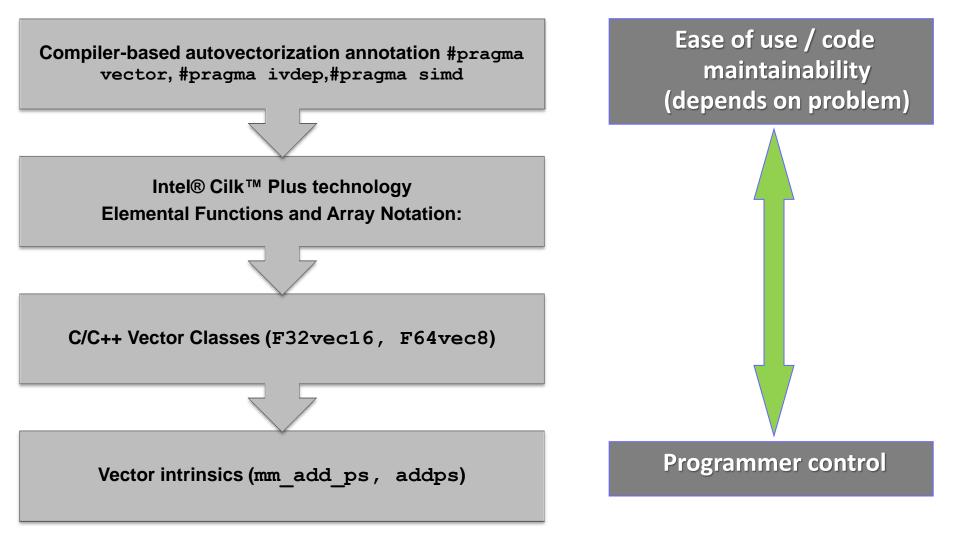

#### **SIMD** Abstraction – Options Compared

Source : References & Intel Xeon-Phi; http://www.intel.com/

C-DAC hyPACK-2013

Xeon-Phi Coprocessors : An Overview

#### Demand vectorization by annotation - #pragma simd

#### Syntax: #pragma simd [<clause-list>]

- Mechanism to force vectorization of a loop

- Programmer: asserts a loop ought to be vectorized

- > Compiler: vectorizes the loop or gives an error

| Clause                                                                               | Semantics                                                                                                                                 |  |  |  |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| No clause                                                                            | Enforce vectorization of innermost loops; ignore dependencies etc                                                                         |  |  |  |

| vectorlength $(n_1[, n_2])$                                                          | Select one or more vector lengths (range: 2, 4, 8, 16) for the vectorizer to use.                                                         |  |  |  |

| private (var <sub>1</sub> , var <sub>2</sub> ,, var <sub>N</sub> )                   | Scalars private to each iteration. Initial value broadcast to all instances. Last value copied out from the last loop iteration instance. |  |  |  |

| linear (var <sub>1</sub> :step <sub>1</sub> ,, var <sub>N</sub> :step <sub>N</sub> ) | Declare induction variables and corresponding positive integer step sizes (in multiples of vector length)                                 |  |  |  |

| reduction (operator: $var_1$ , $var_2$ ,, $var_N$ )                                  | Declare the private scalars to be combined at the end of the loop<br>using the specified reduction operator                               |  |  |  |

| [no]assert                                                                           | Direct compiler to assert when the vectorization fails. Default is to assert for SIMD pragma.                                             |  |  |  |

| Source : References & Intel Xeon-Phi; http://www.intel.com/                          |                                                                                                                                           |  |  |  |

#### **Software Behind the Vectorization**

```

float *restrict A, *B, *C;

for(i=0;i<n;i++) {

A[i] = B[i] + C[i];

}</pre>

```

Vector (or SIMD) Code computes more than one element at a time.

- \* [SSE2] 4 elems at a time

addps xmm1, xmm2

- [AVX] 8 elems at a time

vaddps ymm1, ymm2, ymm3

- [IMCI] 16 elems at a time

vaddps zmm1, zmm2, zmm3

Source : References & Intel Xeon-Phi; http://www.intel.com/

C-DAC hyPACK-2013

#### Hardware resources behind Vectorization

CPU has lot of computation power in form of SIMD unit.

- XMM (128bit) can operate

- ➢ 16x chars

- 8x shorts

- 4x dwords/floats

- 2x qwords/doubles/float complex

- YMM (256bit) can operate

- ➢ 32x chars

- > 16x shorts

- Sx dwords/floats

- 4x qwords/doubles/float complex

- > 2x double complex

- Intel<sup>®</sup> Xeon Phi<sup>™</sup> Coprocessor (512bit) can operate

- 16x chars/shorts (converted to int)

- 16x dwords/floats

- 8x qwords/doubles/float complex

- > 4x double complex

Intel Xeon Phi Coprocessors :

**Compilation and Vectorization**

## Part-2

Compilation

## Intel Xeon-Phi Coprocessor System Access

#### Quick Glance:

- In native mode an application is compiled on the host using the compiler switch -mmic to generate code for the MIC architecture. The binary can then be copied to the coprocessor and has to be started there.

- Vector-Vector-Multiplication

[hypack01@mic-0]\$ icc -03 -mmic vv.c -o vv

[hypack01@mic-0]\$ scp vv mic0:

program 100% 10KB 10.2KB/s 00:00

[hypack01@mic-0]\$ ssh mic0 ~/run

vector-vector Multiplication = 16.00

## Intel Xeon-Phi Coprocessor System Access

#### Quick Glance:

```

In native mode an application is compiled on the host using the compiler switch -mmic to generate code for

```

the MIC architecture. The binary can then be copied to the coprocessor and has to be started there.

[hypack01@mic-0]\$ icc -03 -mmic test.c -o test

[hypack01@mic-0]\$ scp test mic0: program 100% 10KB 10.2KB/s 00:00

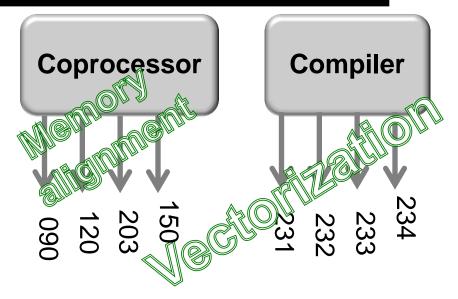

## Intel Xeon Phi Coprocessor :Native Compilation

# To achieve good Performance - Following information should be kept in mind.

- Data should be aligned to 64 Bytes (512 Bits) for the MIC architecture, in contrast to 32 Bytes (256 Bits) for AVX and 16 Bytes (128 Bits) for SSE.

- Due to the large SIMD width of 64 Bytes vectorization is even more important for the MIC architecture than for Intel Xeon!

- The MIC architecture offers new instructions like

- > gather/scatter,

- > fused multiply-add,

- masked vector instructions etc.

which allow more loops to be parallelized on the coprocessor than on an **Intel Xeon based host**.

## Intel Xeon Phi Coprocessor : Native Compilation

To achieve good Performance - Following information should be kept in mind.

Use pragmas like

- > #pragma ivdep,

- > #pragma vector always,

- > #pragma vector aligned,

- > #pragma simd

etc. to achieve autovectorization.

Autovectorization is enabled at default optimization level -02. Requirements for vectorizable loops can be found references.

## Intel Xeon Phi Coprocessor : Native Compilation

# To achieve good Performance - Following information should be kept in mind.

- Let the compiler generate vectorization reports using the compiler option -vecreport2 to see if loops were vectorized for MIC (Message "\*MIC\* Loop was vectorized" etc).

- The options -opt-report-phase hlo (High Level Optimizer Report) or

-opt-report-phase ipo\_inl (Inlining report) may also be useful.

## Intel Xeon Phi Coprocessor :Native Compilation

# To achieve good Performance - Following information should be kept in mind.

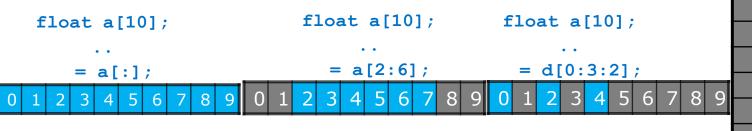

- Explicit vector programming is also possible via Intel Cilk Plus language extensions (C/C++ array notation, vector elemental functions, ...) or the new SIMD constructs from OpenMP 4.0 RC1.

- Vector elemental functions can be declared by using <u>attributes</u> ((vector)). The compiler then generates a vectorized version of a scalar function which can be called from a vectorized loop.

## Intel Xeon Phi Coprocessor : Native Compilation

# To achieve good Performance - Following information should be kept in mind.

- One can use intrinsics to have full control over the vector registers and the instruction set.

- Include <immintrin.h> for using intrinsics.

- ✤ Hardware prefetching from the L2 cache is enabled per default.

- In addition, software prefetching is on by default at compiler optimization level -O2 and above. Since Intel Xeon Phi is an inorder architecture, care about prefetching is more important than on out-of-order architectures.

## Intel Xeon Phi Coprocessor : Native Compilation

To achieve good Performance - Following information should be kept in mind.

The compiler prefetching can be influenced by setting the compiler switch -opt-prefetch = n.

Manual prefetching can be done by using intrinsics (\_mm\_prefetch()) or

pragmas (**#pragma prefetch var**).

- Simply add OpenMP-like pragmas to C/C++ or Fortran code to mark regions of code that should be offloaded to the Intel Xeon Phi Coprocessor and be run there.

- This approach is quite similar to the accelerator pragmas introduced by the

- > NVIDIA PGI compiler,

- CAPS HMPP or

- OpenACC to offload code to GPGPUs.

#### Work done – Compiler's Offload

- When the Intelcompiler encounters an offload pragma, it generates code for both the coprocessor and the host.

- 2. Code to transfer the data to the coprocessor is automatically created by the compiler,

- 3. The programmer can influence the data transfer by adding data clauses to the offload pragma.

#### Details can be found under "Offload Using a Pragma" in the Intel compiler documentation.

A simple example how to offload a **matrix-matrix computation** to the coprocessor. (*No function or subroutine*) is included

```

main() {

double *a, *b, *c;

int i,j,k, ok, n=100;

// allocated memory on the heap aligned to 64 byte boundary

ok = posix memalign((void**)&a, 64, n*n*sizeof(double));

```

- ok = posix memalign((void\*\*)&b, 64, n\*n\*sizeof(double));

- ok = posix\_memalign((void\*\*)&c, 64, n\*n\*sizeof(double));

```

// initialize matrices

```

Code " *Simple example for matrix-matrix computation*" – may not give good performance on all cores

```

//offload code

#pragma offload target(mic) in(a,b:length(n*n))

inout(c:length(n*n))

//parallelize via OpenMP on MIC

#pragma omp parallel for

for(i = 0; i < n; i++) {

for( k = 0; k < n; k++ ) {

#pragma vector aligned

#pragma ivdep

for (j = 0; j < n; j++) {

//c[i][j] = c[i][j] + a[i][k]*b[k][j];

c[i*n+j] = c[i*n+j] + a[i*n+k]*b[k*n+j];

}

Code " Simple example for matrix-matrix computation" – May

}

not give good performance on all cores

```

#### **Summary of Example Program**

- 1. Shows how to offload the matrix computation to the coprocessor using the **#pragma offload target(mic**).

- One could also specify the specific coprocessor num in a system with multiple coprocessors by using #pragma offload target(mic:num)

- 3. Matrices have been dynamically allocated using posix\_memalign(), their sizes must be specified via the length() clause.

It is recommended that for Intel Xeon Phi data is 64-byte aligned

#### Summary of Example Program

- 1. Shows how to offload the matrix computation to the coprocessor using the **#pragma offload target(mic**).

- 1. **#pragma vector aligned** tells the compiler that all array data accessed in the loop is properly aligned.

- 2. **#pragma ivdep** discards any data dependencies assumed by the compiler

Offloading is enabled per default for the Intel compiler. Use **-no-offload** to disable the generation of offload code.

#### **Obtain Offload Information about the following**

Using the compiler option -vec-report2, one can see which loops have been vectorized on the host & the MIC coprocessor: [hypack01@mic-0]\$ icc -vec-report2 -openmp offload.c

offload.c(57): (col. 2) remark: loop was not vectorized: vectorization possible but seems inefficient.

```

offload.c(57):(col. 2) remark: *MIC* LOOP WAS VECTORIZED.

offload.c(54):(col. 7) remark: *MIC* loop was not

vectorized: not inner loop.

offload.c(53): (col. 5) remark: *MIC* loop was not

vectorized: not inner loop.

```

Mind the **C99** restrict keyword that specifies that the vectors do not overlap. (Compile with -std=c99)

C-DAC hyPACK-2013 Xeon-Ph

#### **Obtain Offload Information about the following**

By setting the environment variable **OFFLOAD REPORT** one can obtain information about per.& data transfers at runtime:

```

[hypack01@mic-0]$ export OFFLOAD_REPORT=2

[hypack01@mic-0]$ ./a.out

```

```

[Offload] [MIC 0] [File] offload2.c

```

```

[Offload] [MIC 0] [Line] 50

```

```

[Offload] [MIC 0] [CPU Time] 12.853562 (seconds)

```

```

[Offload] [MIC 0] [CPU->MIC Data] 9830416 (bytes)

```

```

[Offload] [MIC 0] [MIC Time] 12.208636 (seconds)

```

```

[Offload] [MIC 0] [MIC->CPU Data] 3276816 (bytes)

```

```

offload.c(53): (col. 5) remark: *MIC* loop was not

vectorized: not inner loop.

```

A simple example how to offload a **matrix-matrix computation** to the coprocessor. (*No function or subroutine*) is included

If a function is called within the offloaded code block, this function has to be declared with

#### \_attribute\_\_((target(mic)))

to disable the generation of offload code.

Code " *Simple example for matrix-matrix computation*" – may not give good performance on all cores

```

A simple example how to offload a matrix-matrix computation a

subroutine and call that routine within an offloaded block region:

attribute__((target(mic))) void mxm( int n, \

double *restrict a, double * restrict b, \setminus

double *restrict c ) {

int i,j,k;

for(i = 0; i < n; i++) {

main() {

#pragma offload target(mic) \

in(a,b:length(n*n)) inout(c:length(n*n))

mxm(n,a,b,c);

C-DAC hyPACK-2013

```

#### **Syntax of Programs**

| Pragma                               | Syntax                                                                                   | Semantic                                                                                        |

|--------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|                                      | C++                                                                                      |                                                                                                 |

| Offload pragma                       | <pre>#pragma offload <clauses> <statement></statement></clauses></pre>                   | Allow next statement to<br>execute on coprocessor or<br>host CPU                                |

| Variable/function offload properties | _attribute<br>((target(mic)))                                                            | Compile function for, or<br>allocate variable on, both<br>host CPU and coprocessor              |

| Entire blocks of<br>data/code defs   | <pre>#pragma offload_attribute(pus h, target(mic)) #pragma offload_attribute(pop )</pre> | Mark entire files or large<br>blocks of code to compile<br>for both host CPU and<br>coprocessor |

#### **Syntax of Programs**

| Pragma                               | Syntax                                                                                                 | Semantic                                                                                     |

|--------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|                                      | Fortran                                                                                                |                                                                                              |

| Offload directive                    | !dir\$ omp offload<br><clauses> <statement></statement></clauses>                                      | Execute OpenMP parallel block on coprocessor                                                 |

| Variable/function offload properties | <pre>!dir\$ attributes offload:<mic> :: <ret-name> OR <var1,var2,></var1,var2,></ret-name></mic></pre> | Compile function or variable for CPU and coprocessor                                         |

| Entire code blocks                   | !dir\$ offload begin<br><clauses><br/><br/>!dir\$ end offload</clauses>                                | Mark entire files or large<br>blocks of code to compile<br>for both host CPU and coprocessor |

#### Syntax of Programs

The following clauses can be used to control data transfers:

| Clause                | Syntax                        | Semantic                                                       |

|-----------------------|-------------------------------|----------------------------------------------------------------|

| Multiple coprocessors | <pre>target(mic[:unit])</pre> | Select specific coprocessors                                   |

| Inputs                | in(var-list<br>modifiers)     | Copy from host to coprocessor                                  |

| Outputs               | out(var-list<br>modifiers)    | Copy from coprocessor to host                                  |

| Inputs & Outputs      | inout(var-list<br>modifiers)  | Copy host to coprocessor<br>and back when offload<br>completes |

| Non-copied data       | nocopy(var-list<br>modifiers) | Data is local to target                                        |

#### Syntax of Programs

The following (optional) modifiers are specified:

| Modifier                 | Syntax               | Semantic                          |

|--------------------------|----------------------|-----------------------------------|

| Specify copy length      | length(N)            | Copy N elements of                |

|                          |                      | pointer's type                    |

| Coprocessor memory       | alloc_if ( bool )    | Allocate coprocessor space        |

| allocation               |                      | on this offload (default:         |

|                          |                      | TRUE)                             |

| Coprocessor memory       | free_if ( bool )     | Free coprocessor space at         |

| release                  |                      | the end of this offload (default: |

|                          |                      | TRUE)                             |

| Control target data      | align ( N bytes )    | Specify minimum memory            |

| alignment                |                      | alignment on coprocessor          |

| Array partial allocation | alloc (array-slice ) | Enables partial array allocation  |

| & variable relocation    | into ( var-expr )    | and data copy into                |

|                          |                      | other vars & ranges               |

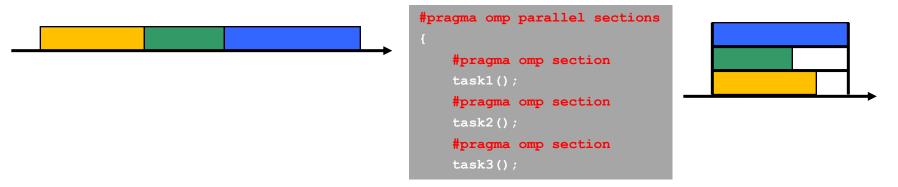

#### **Explicit Worksharing**

```

#pragma omp parallel

#pragma omp sections

#pragma omp section

//section running on the coprocessor

#pragma offload target(mic) in(a,b:length(n*n)) inout(c:length(n*n))

mxm(n,a,b,c);

#pragma omp section

//section running on the host

mxm(n,d,e,f);

```

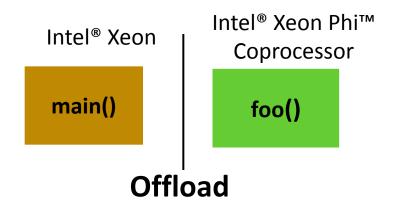

#### Persistent data on the coprocessor

- The main bottleneck of accelerator based programming are data transfers over the slow PCIe bus from the host to the accelerator and vice versa.

- To increase the performance one should minimize data transfers as much as possible and keep the data on the coprocessor between computations using the same data.

- Defining the following macros #define ALLOC alloc\_if(1) #define FREE free\_if(1) #define RETAIN free\_if(0) #define REUSE alloc\_if(0)

#### Persistent data on the coprocessor

- The main bottleneck of accelerator based programming are data transfers over the slow PCIe bus from the host to the accelerator and vice versa.

- one can simply use the following notation: to allocate data and keep it for the next offload

#### #pragma offload target(mic)in (p:length(l) ALLOC RETAIN)

to reuse the data and still keep it on the coprocessor

#pragma offload target(mic)in (p:length(l) REUSE RETAIN)

to reuse the data again and free the memory. (FREE is the default, and does not need to be explicitly specified)

#pragma offload target(mic) in (p:length(1) REUSE FREE)

More information can be found in the section "Managing Memory Allocation for Pointer Variables" under "Offload Using a Pragma"

#### **Optimised Offloaded Code**

- Optimizing offloaded code

- The implementation of the matrix-matrix multiplication can be optimized by defining appropriate ROWCHUNK and COLCHUNK chunk sizes.

- Rewrite the code with 6 nested loops (using OpenMP col-apse for the 2 outermost loops) and some manual loop unrolling

#### **Optimizing Offloaded Code**

```

#define ROWCHUNK 96

#define COLCHUNK 96

#pragma omp parallel for collapse(2) private(i,j,k)

for(i = 0; i < n; i+=ROWCHUNK) {

for(j = 0; j < n; j+=ROWCHUNK) {

for(k = 0; k < n; k+=COLCHUNK) {

for (ii = i; ii < i+ROWCHUNK; ii+=6) {

for (kk = k; kk < k+COLCHUNK; kk++ ) {

}

}</pre>

```

#### #pragma ivdep

#### #pragma vector aligned

```

for ( jj = j; jj < j+ROWCHUNK; jj++) {

c[(ii*n)+jj] += a[(ii*n)+kk]*b[kk*n+jj];

c[((ii+1)*n)+jj] += a[((ii+1)*n)+kk]*b[kk*n+jj];

c[((ii+2)*n)+jj] += a[((ii+2)*n)+kk]*b[kk*n+jj];

c[((ii+3)*n)+jj] += a[((ii+3)*n)+kk]*b[kk*n+jj];

c[((ii+4)*n)+jj] += a[((ii+5)*n)+kk]*b[kk*n+jj];

c[((ii+5)*n)+jj] += a[((ii+5)*n)+kk]*b[kk*n+jj];

}

}</pre>

```

Intel Xeon Phi Coprocessors :

**Compilation and Vectorization**

# Part-2

# **Compiler-based Vectorization**

# **Use Compiler Optimization Switches**

| Optimization Done                              | Linux*                                                              |

|------------------------------------------------|---------------------------------------------------------------------|

| Disable optimization                           | -00                                                                 |

| Optimize for speed (no code size increase)     | -01                                                                 |

| Optimize for speed (default)                   | -02                                                                 |

| High-level loop optimization                   | -03                                                                 |

| Create symbols for debugging                   | -g                                                                  |

| Multi-file inter-procedural optimization       | -ipo                                                                |

| Profile guided optimization (multi-step build) | -prof-gen<br>-prof-use                                              |

| Optimize for speed across the entire program   | <b>-fast</b><br>(same as: -ipo –O3 -no-<br>prec-div -static -xHost) |

| OpenMP 3.0 support                             | -openmp                                                             |

| Automatic parallelization                      | -parallel                                                           |

## **Compiler Reports – Optimization Report**

**Compiler switch:** -opt-report-phase[=phase]

phase can be:

- ipo\_inl Interprocedural Optimization Inlining Report

- ilo Intermediate Language Scalar Optimization

- hpo High Performance Optimization

- hlo High-level Optimization

- all All optimizations (not recommended, output too verbose)

#### Control the level of detail in the report:

-opt-report[0|1|2|3]

If you do not specify the option, no optimization report is being generated; if you do not specify the level (i.e. -opt-report) level 2 is being used by the compiler.

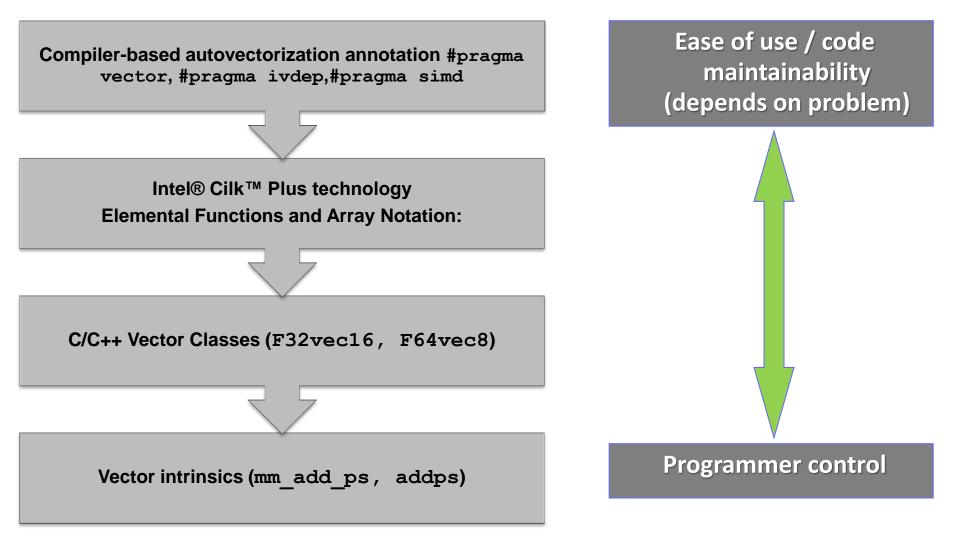

# **Compiler-Based Autovectorization**

- Compiler recreate vector instructions from the serial Program

- Compiler make decisions based on some assumption

- The programmer reassures the compiler on those assumptions

- The compiler takes the directives and compares them with its analysis of the code

#pragma simd

- Compiler checks for

- Is "\*p" loop invariant?

- Are a, b, and c loop invariant?

```

#pragma simd

reduction(+:sum)

for(i=0;i<*p;i++) {

a[i] = b[i]*c[i];

sum = sum + a[i];

}</pre>

```

- Does a[] overlap with b[], c[], and/or sum?

- Is "+" operator associative? (Does the order of "add"s matter?)

- Vector computation on the target expected to be faster than scalar code?

#### Compiler checks for

- Is "\*p" loop invariant?

- > Are a, b, and c loop invariant?

- Does a[] overlap with b[], c[], and/or sum?

- Is "+" operator associative? (Does the order of "add"s matter?)

- Vector computation on the target expected to be faster than scalar code?

## Compiler Confirms this loop :

- "\*p" is loop invariant

- ➤ a[] is not aliased with b[], c[], and sum

- > sum is not aliased with b[] and c[]

- "+" operation on sum is associative (Compiler can reorder the "add"s on sum)

- Vector code to be generated even if it could be slower than scalar code

## **Compiler-Based Autovectorization**

- Compiler recreate vector instructions from the serial Program

- Compiler make decisions based on some assumption

- The programmer reassures the compiler on those assumptions

- > The compiler takes the directives and compares them with its analysis of the code

- Compiler checks for

- Is "\*p" loop invariant?

- Are a, b, and c loop invariant?

- Does a[] overlap with b[], c[], and/or sum?

- Is "+" operator associative? (Does the order of "add"s matter?)

- Vector computation on the target expected to be faster than scalar code?

- Compiler Confirms this loop :

- "\*p" is loop invariant

- a[] is not aliased with b[], c[], and sum

- sum is not aliased with b[] and c[]

- "+" operation on sum is associative (Compiler can reorder the "add"s on sum)

- Vector code to be generated even if it could be slower than scalar code Source : References & Intel Xeon-Phi; <u>http://www.intel.com/</u>

#pragma simd reduction(+:sum)

for(i=0;i<\*p;i++) {

a[i] = b[i]\*c[i];</pre>

sum = sum + a[i];

# Hints to Compiler for Vectorization Opportunities

| #pragma                                   | Semantics                                                                                                                                                                                               |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #pragma ivdep                             | Ignore vector dependences unless they are proven by the compiler                                                                                                                                        |

| <pre>#pragma vector always [assert]</pre> | If the loop is vectorizable, ignore any benefit<br>analysis<br>If the loop did not vectorize, give a compile-time<br>error message via assert                                                           |

| #pragma novector                          | Specifies that a loop should never be vectorized,<br>even if it is legal to do so, when avoiding<br>vectorization of a loop is desirable (when<br>vectorization results in a performance<br>regression) |

# Hints to Compiler for Vectorization Opportunities

| #pragma                                       | Semantics                                                                                                                                                                                                |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>#pragma vector aligned / unaligned</pre> | instructs the compiler to use<br>aligned (unaligned) data movement<br>instructions for all array references<br>when vectorizing                                                                          |

| #pragma vector temporal<br>/ nontemporal      | directs the compiler to use<br>temporal/non-temporal (that is,<br>streaming) stores on systems based<br>on IA-32 and Intel® 64<br>architectures; optionally takes a<br>comma separated list of variables |

# Hints to Compiler for Vectorization

| #pragma                                          | Semantics                                                                                                                                                                                                      |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #pragma ivdep                                    | Ignore vector dependences unless they are proven by the compiler                                                                                                                                               |

| <pre>#pragma vector always [assert]</pre>        | If the loop is vectorizable, ignore any benefit analysis<br>If the loop did not vectorize, give a compile-time error<br>message via assert                                                                     |

| #pragma novector                                 | Specifies that a loop should never be vectorized, even if it<br>is legal to do so, when avoiding vectorization of a loop is<br>desirable (when vectorization results in a performance<br>regression)           |

| <pre>#pragma vector aligned / unaligned</pre>    | instructs the compiler to use aligned (unaligned) data<br>movement instructions for all array references when<br>vectorizing                                                                                   |

| <pre>#pragma vector temporal / nontemporal</pre> | directs the compiler to use temporal/non-temporal (that<br>is, streaming) stores on systems based on IA-32 and Intel <sup>®</sup><br>64 architectures; optionally takes a comma separated list<br>of variables |

# **Compiler VEC report**

- Indicates whether each loop is vectorized

- ➤ Vectorized ≠ efficient

- Different levels

- -vec-report1, for high-level triage of large code

- -vec-report2, when you want reasons for not vectorizing

- -vec-report6, for even more detail, e.g. misalignment

- Indicates reasons for not vectorizing

- > Unsupported datatype  $\rightarrow$  rewrite to use 32b indices vs. 64b

- Line numbers may not be what you expect

- Inlining

- Loop distribution, interchange, unrolling, collapsing

## **Compiler OPT report - contents**

- Control over static reports

- -opt-report [n=0-3] enables varying levels of detail

- -opt-report-phase=[several options] enables specific detail

- Reveals info on various compiler optimization

- > Offloaded variables, –opt-report-phase=offload

- Inlining, Vectorization

- > OpenMP parallelization, auto-parallelization

- Loop permutations, loop distribution, loop distribution

- Multiversioning of loops performed by compiler

- Dynamic dependence checking, unit-stride for assumed shape arrays, tripcount checks, etc.

- > Prefetching

- Blocking, unrolling, jamming

- > Whole-program optimization

# **Use Compiler Optimization Switches**

```

#include <math.h>

void quad(int length, float *a, float *b, float *c, \setminus

float *restrict x1, float *restrict x2)

{

for (int i=0; i<length; i++) {</pre>

float s = b[i]*b[i] - 4*a[i]*c[i];

if (s \ge 0) {

s = sqrt(s);

x2[i] = (-b[i]+s)/(2.*a[i]);

x1[i] = (-b[i]-s)/(2.*a[i]);

}

else {

x2[i] = 0.;

x1[i] = 0.;

}

>cc -c -restrict -vec-report2 quad.cpp

> quad5.cpp(5) (col. 3): remark: LOOP WAS VECTORIZED.

```

# Get Your Code Vectorized by Intel Compiler

- Data Layout, AOS -> SOA

- Data Alignment (next slide)

- Make the loop innermost

- ✤ Function call in treatment

- Inline yourself

- inline! Use \_\_forceinline

- Define your own vector version

- Call vector math library SVML

- Adopt jumpless algorithm

- Read/Write is OK if it's continuous

- Loop carried dependency

#### Not a true dependency

```

for(int i = TIMESTEPS; i > 0; i--)

#pragma simd

#pragma unroll(4)

for(int j = 0; j <= i - 1; j++)

cell[j]=puXDf*cell[j+1]+pdXDf*cell[j];

CallResult[opt] = (Basetype)cell[0];</pre>

```

| Array of Structures |    |    |

|---------------------|----|----|

| S0                  | X0 | Т0 |

| S1                  | X1 | T1 |

|                     |    |    |

| Structure of Arrays |    |  |

|---------------------|----|--|

| S0                  | S1 |  |

| X0                  | X1 |  |

| S0                  | S1 |  |

#### A true dependency

```

for (j=1; j<MAX; j++)

a[j] = a[j] + c * a[j-n];</pre>

```

# **Prefetch on Intel Multicore and Manycore**

- Objective: Move data from memory to L1 or L2 Cache in anticipation of CPU Load/Store

- More import on in-order Intel Xeon Phi Coprocessor

- Less important on out of order Intel Xeon Processor

- Compiler prefetching is on by default for Intel<sup>®</sup> Xeon Phi<sup>™</sup> coprocessors at −O2 and above

- Compiler prefetch is not enabled by default on Intel<sup>®</sup> Xeon<sup>®</sup>

Processors

- > Use external options -opt-prefetch[=n] n = 1.. 4

- Use the compiler reporting options to see detailed diagnostics of prefetching per loop

- > Use -opt-report-phase hlo -opt-report 3

## **Automatic Prefetches**

## Loop Prefetch

- Compiler generated prefetches target memory access in a future iteration of the loop

- Target regular, predictable array and pointer access

#### Interactions with Hardware prefetcher

- ☆ Intel<sup>®</sup> Xeon Phi<sup>™</sup> Comprocessor has a hardware L2 prefetcher

- If Software prefetches are doing a good job, Hardware prefetching does not kick in

- References not prefetched by compiler may get prefetched by hardware prefetcher

# **Explicit Prefetch**

## Use Intrinsics

> \_mm\_prefetch((char \*) &a[i], hint);

See xmmintrin.h for possible hints (for L1, L2, non-temporal, ...)

- But you have to specify the prefetch distance

- Also gather/scatter prefetch intrinsics, see zmmintrin.h and compiler user guide, e.g. \_mm512\_prefetch\_i32gather\_ps

## Use a pragma / directive (easier):

- > #pragma prefetch a [:hint[:distance]]

- You specify what to prefetch, but can choose to let compiler figure out how far ahead to do it.